数字电子技术

进制转换

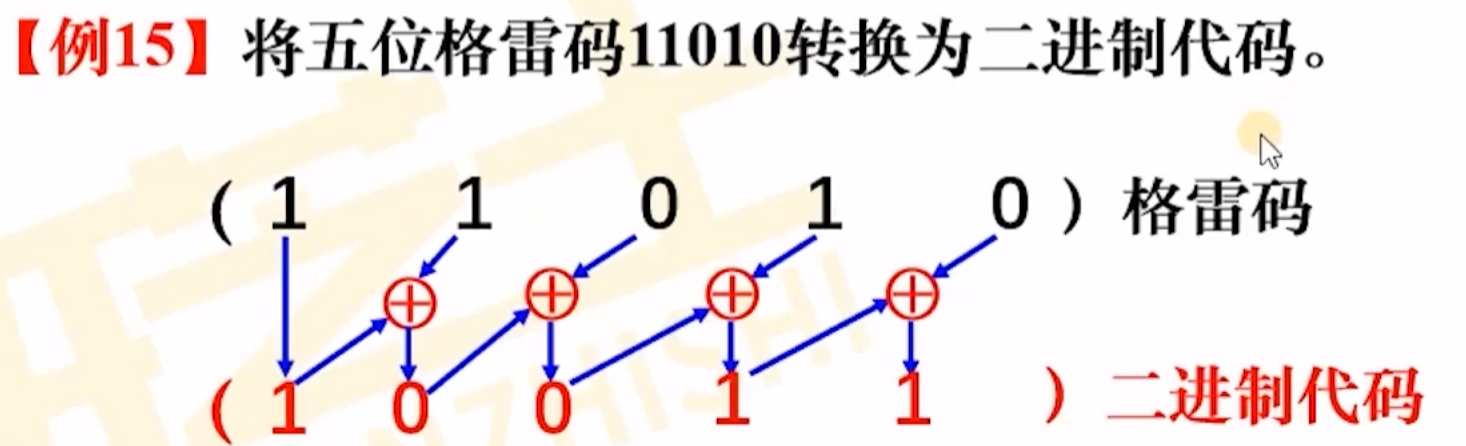

编码

- 原码

用符号位表示二进制数的正负,这种形式的数称为原码。

最高位作为符号位,0表示正,1表示负。正数的反码、补码与原码相同。

- 负数的反码和补码

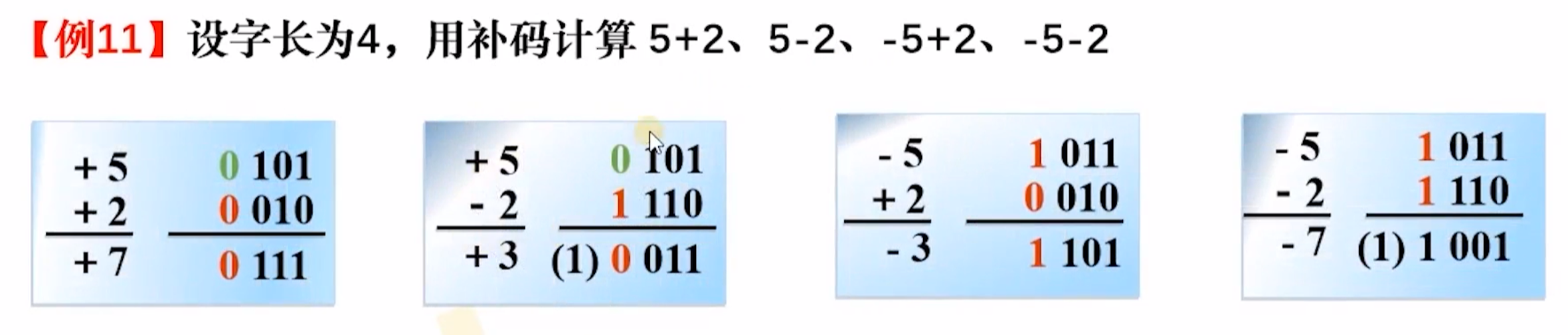

① 符号位不变,数值部分按位求反,就得到了反码。

② 反码+1(符号位不变),即得补码。

③ 补码的补码等于原码。故由补码求原码,就是求补码的补码。

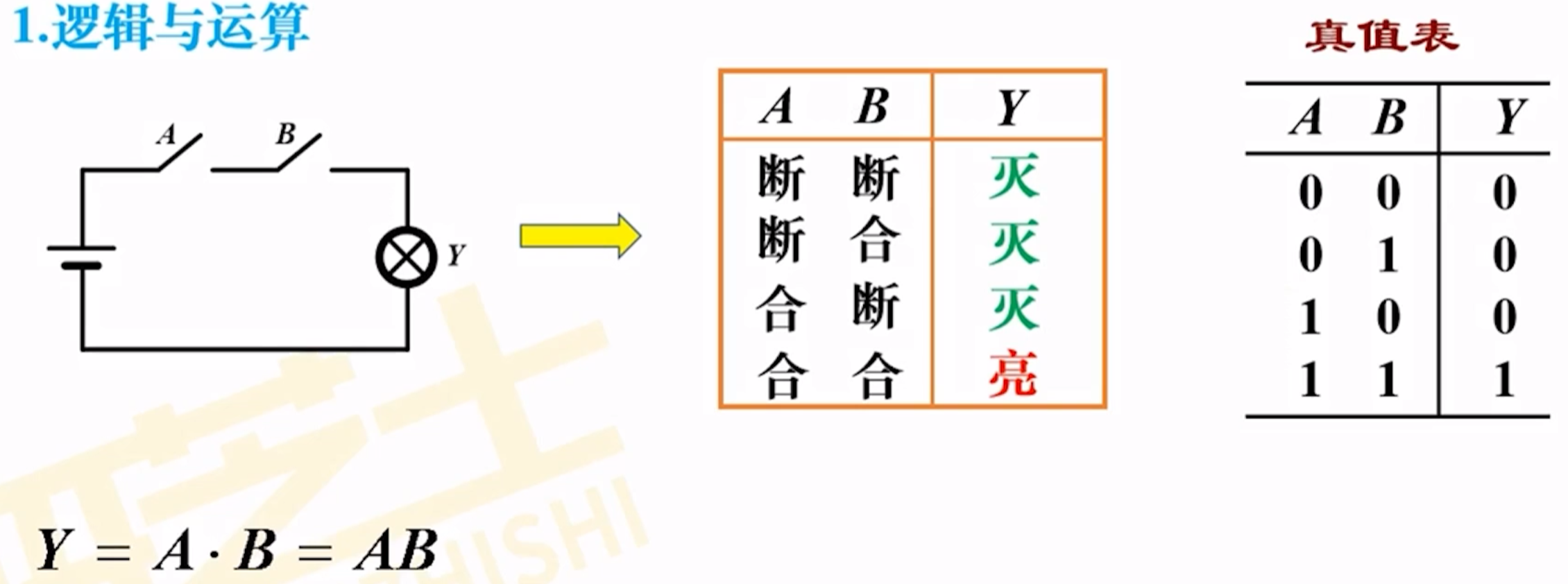

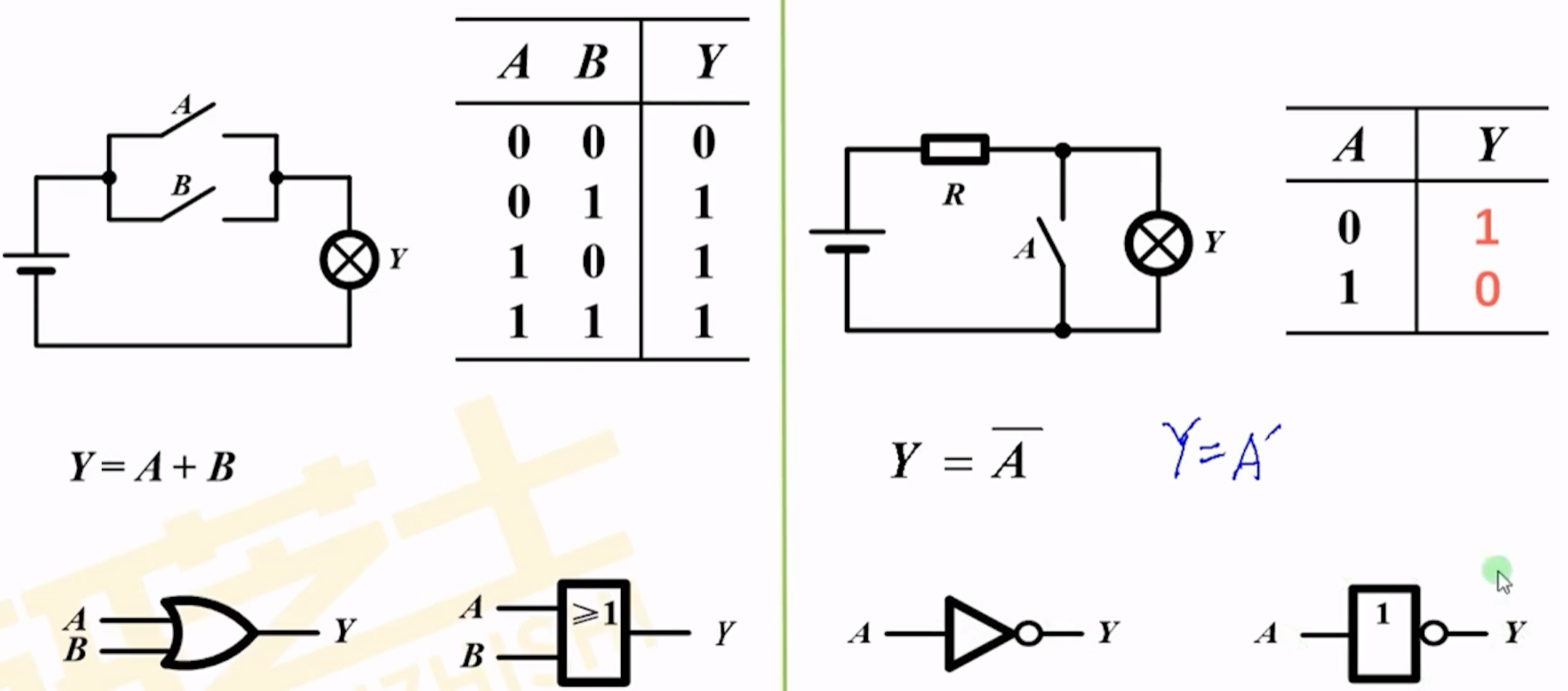

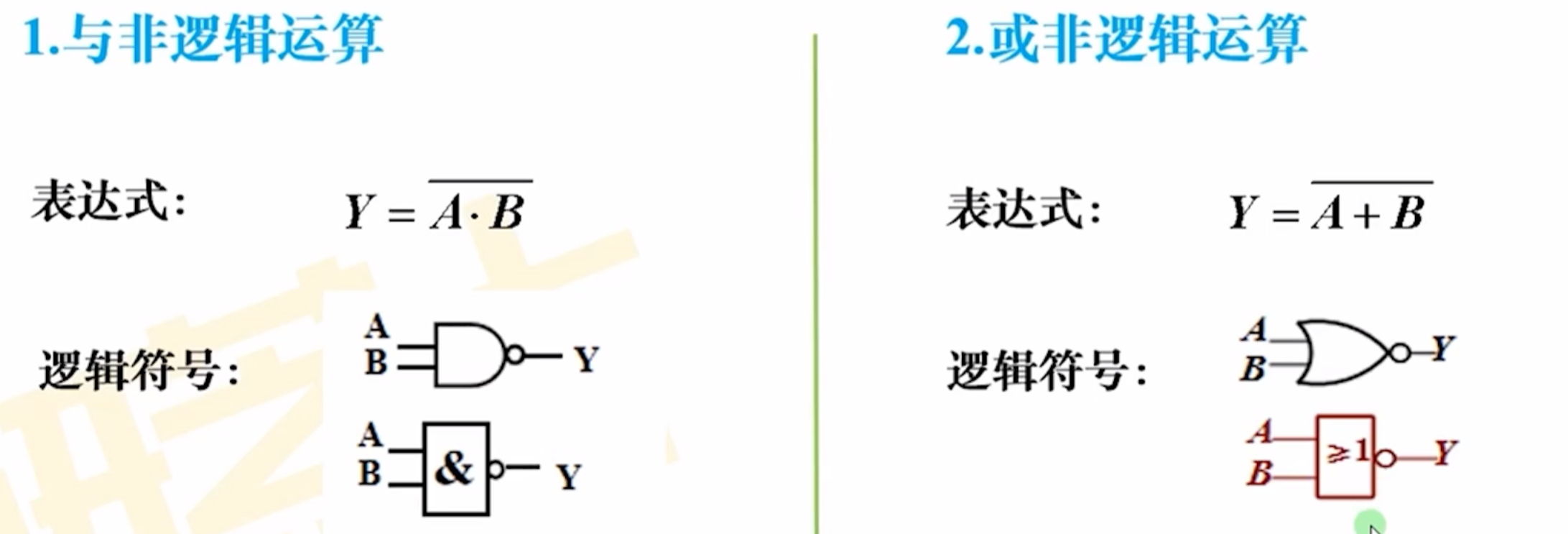

逻辑运算与门电路

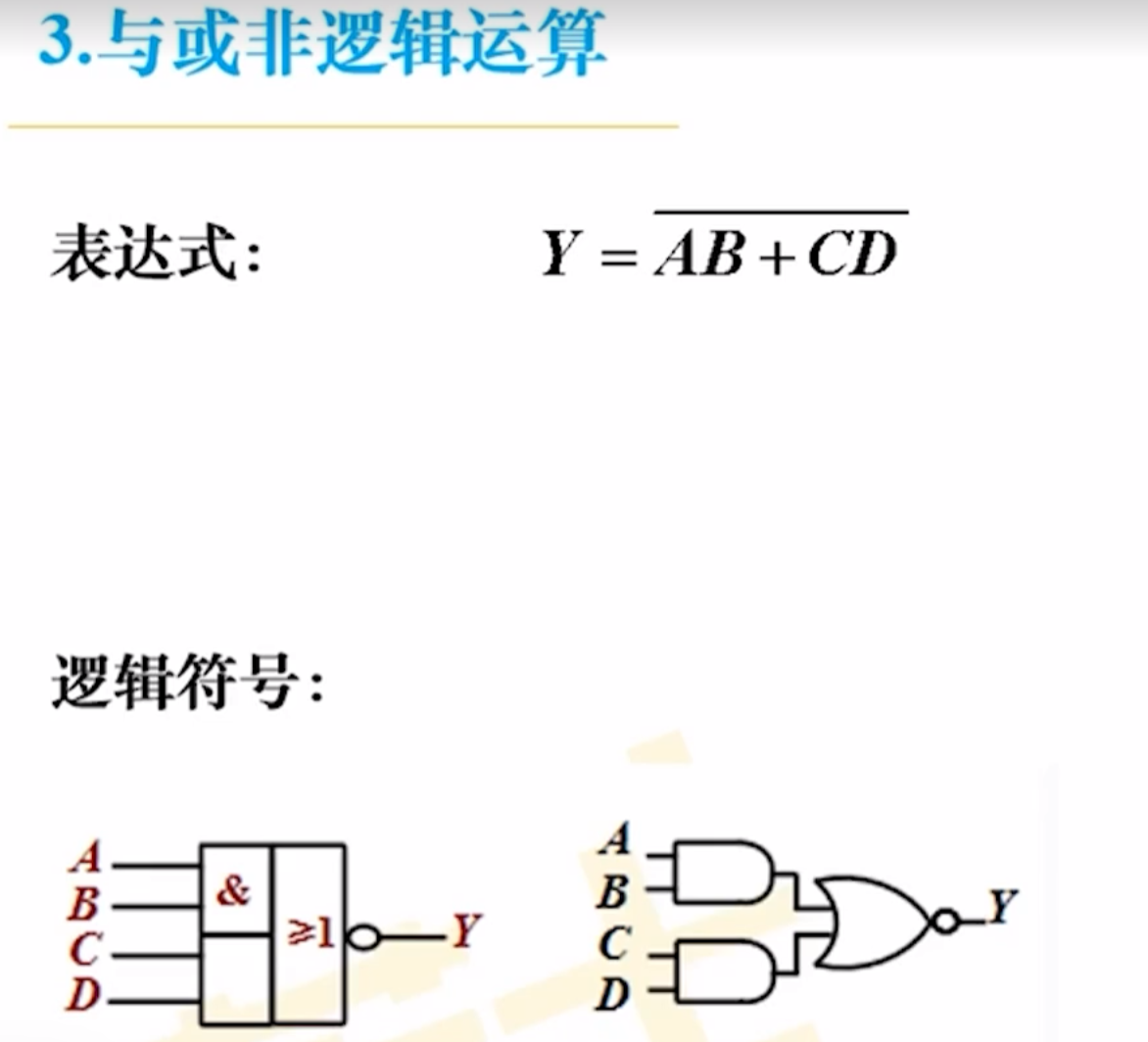

与或非

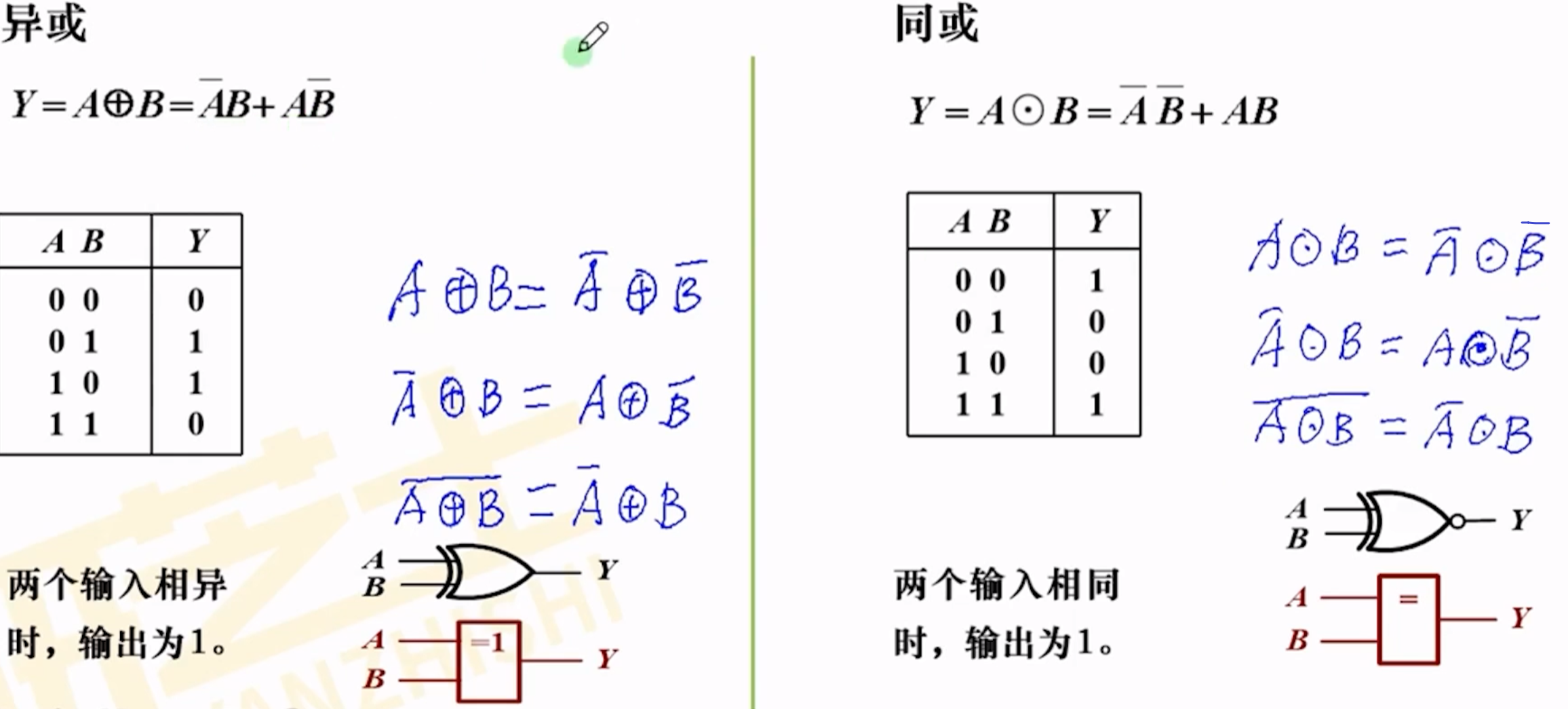

A和1同或是A,A和0同或是A非

A和1同或是A,A和0同或是A非

找AB同时为1的项和CD同时为1的项结果为0,其他结果为1,可快速求出真值表。

找AB同时为1的项和CD同时为1的项结果为0,其他结果为1,可快速求出真值表。

【总结】可通过分析逻辑表达式逻辑功能,快速写出对应的真值表

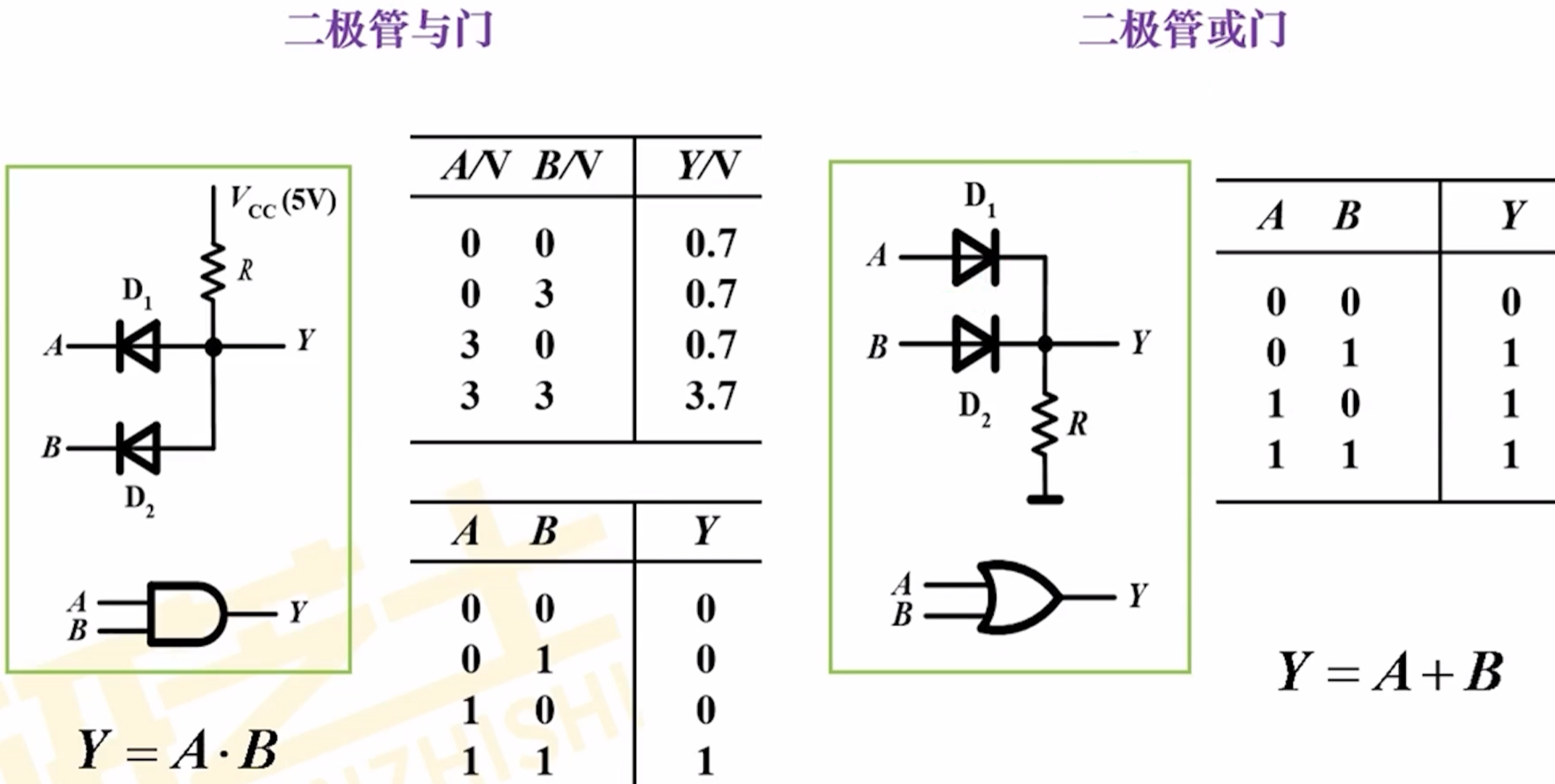

门电路

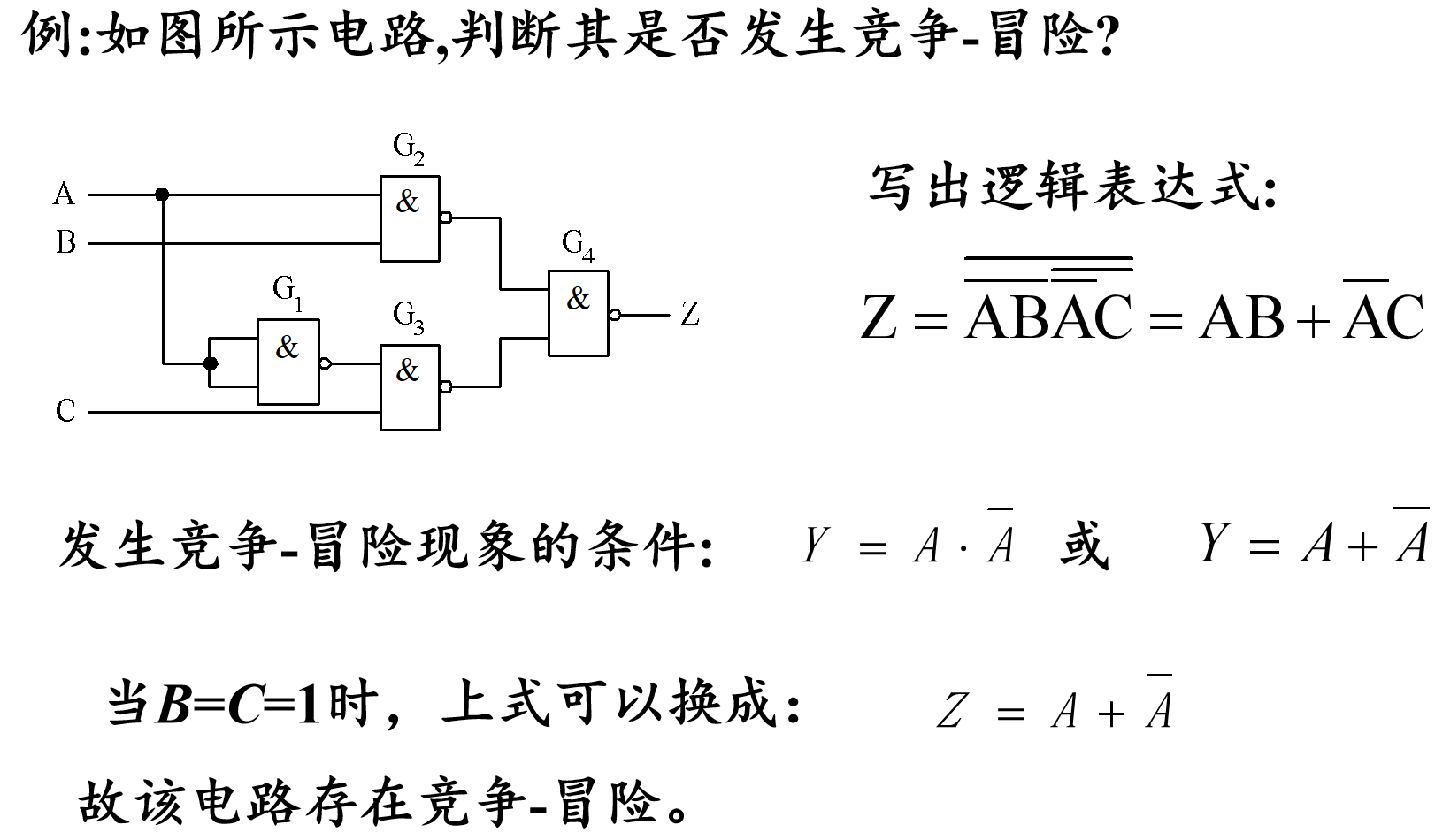

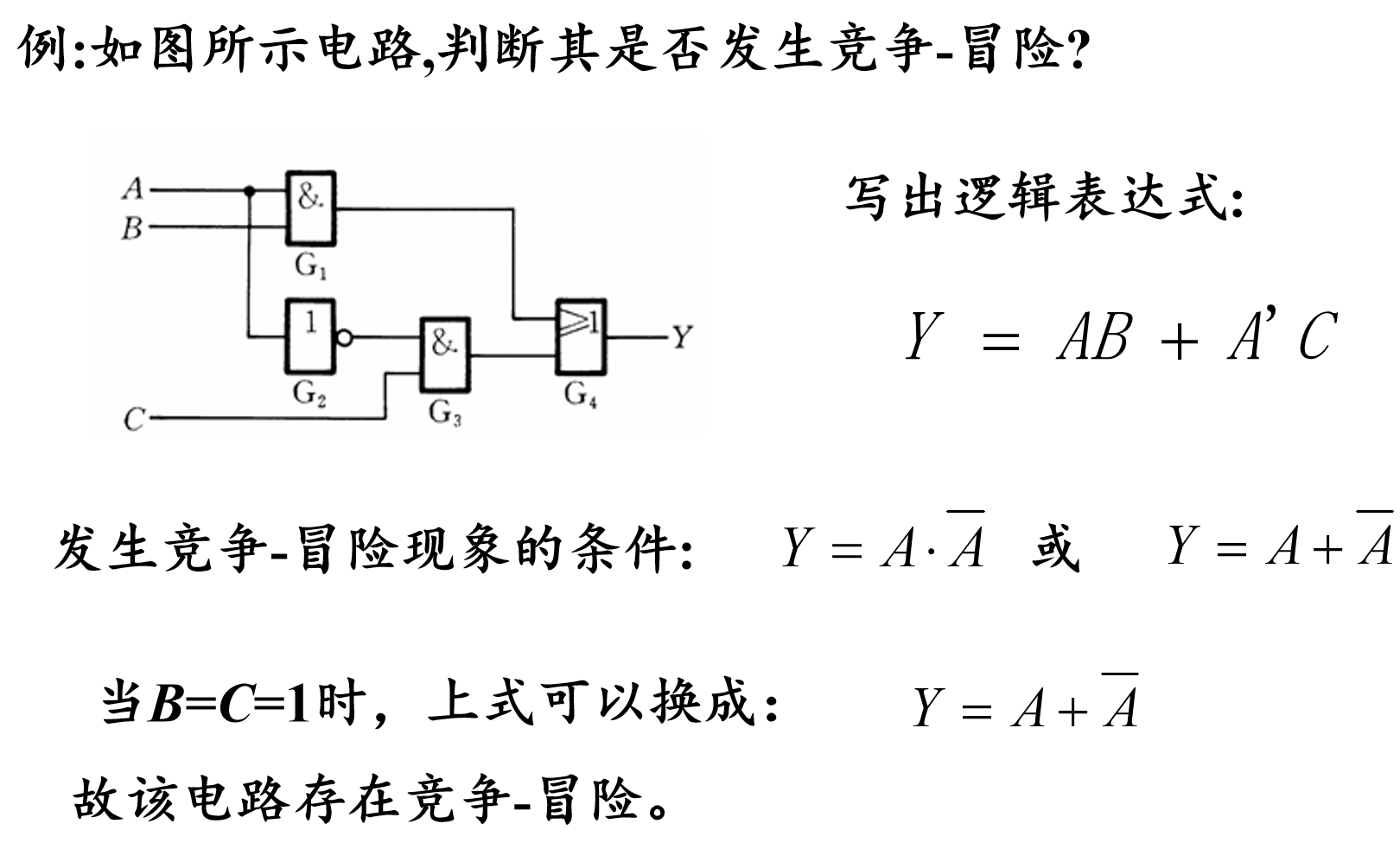

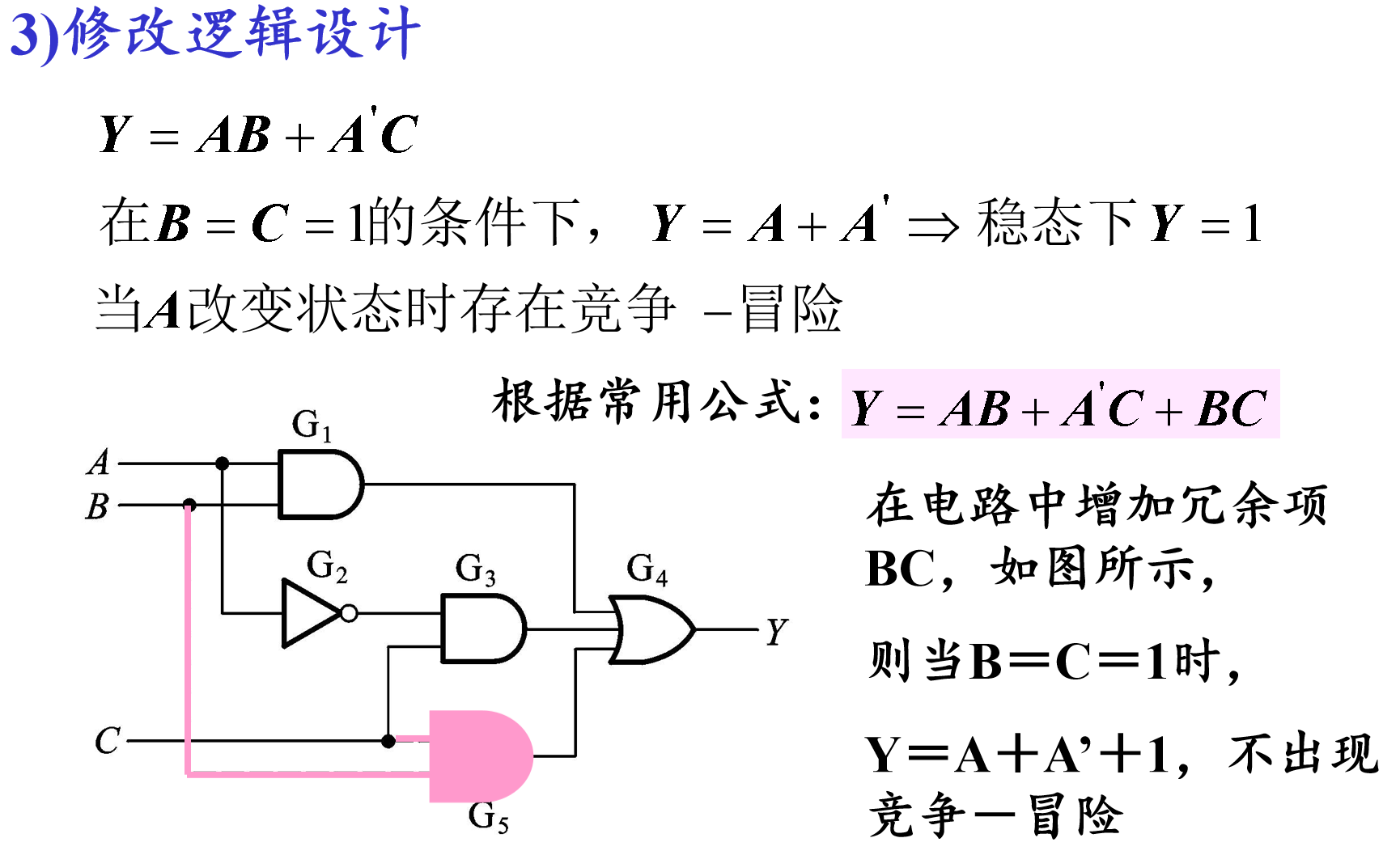

竞争冒险

1型冒险

AA' = 0

0型冒险

A+A' = 0

消除冒险

逻辑代数

基本定律

01律

1.或运算 A + 0 = A

A + 1 = 1

A + A = A

A + A` = 1

2.与运算

A

A

A

A

交换律

A + B = B + A

A

结合律

A + (B + C ) = (A + B) + C

A

分配律

A

A + BC = (A + B)

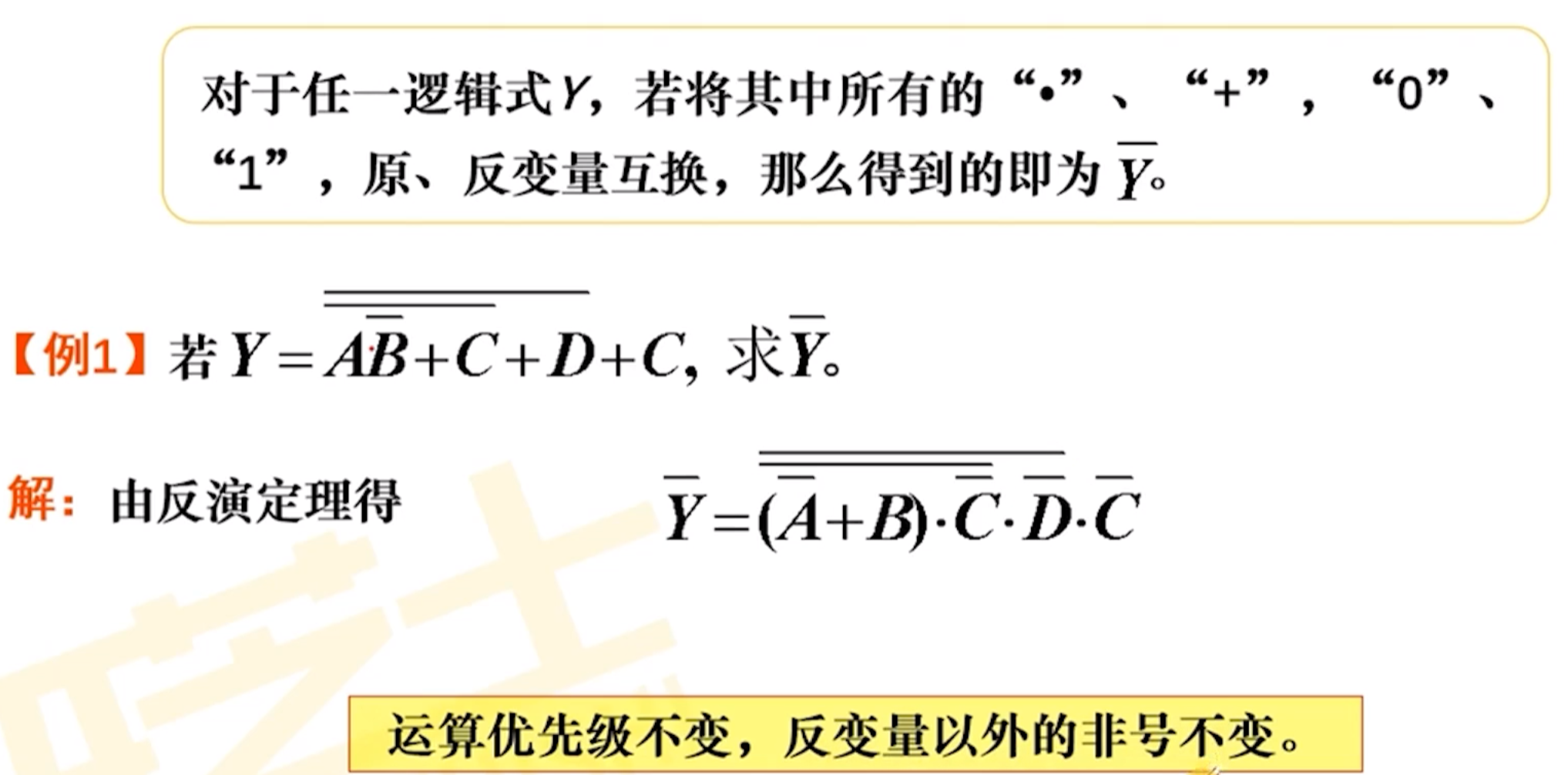

反演律

(A + B)' = A'

(A

(A + B + C +

(A

吸收律

A + AB = A

A(A + B) = A

A + A'B = A + B

(A + B)(A + C) = A + BC

AB + A'C + BC = AB + A'C

AB + A'C + BCD

(A + B)(A' + C)(B + C +

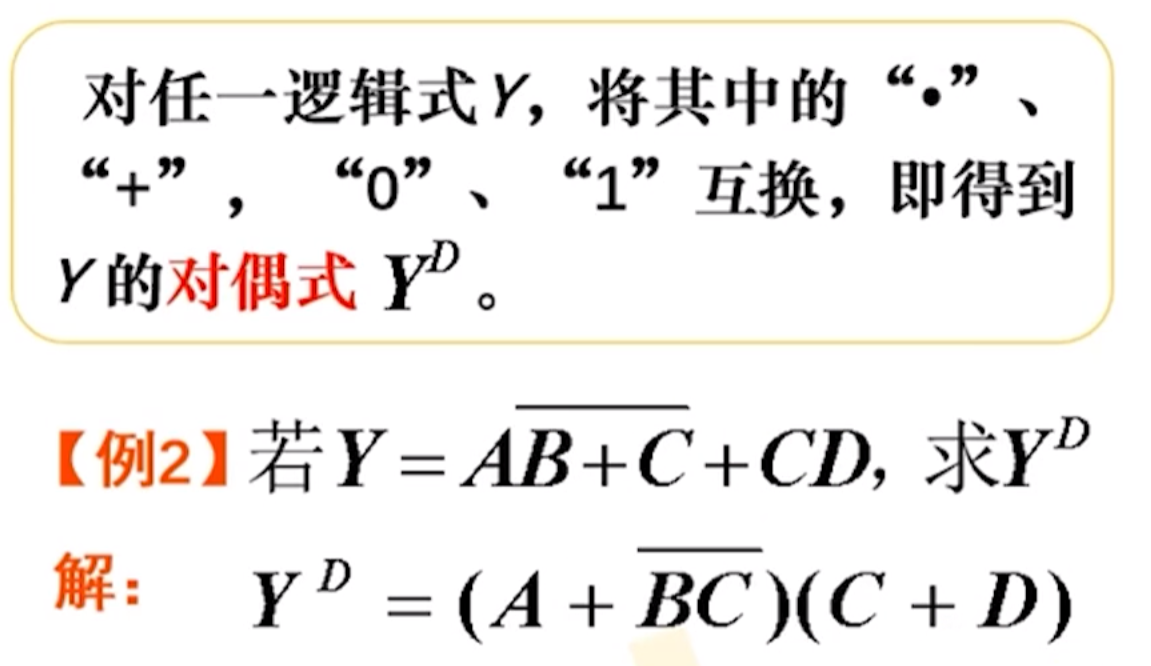

对偶规则 若两逻辑式相等,则对应的对偶式也相等

若两逻辑式相等,则对应的对偶式也相等

最小项

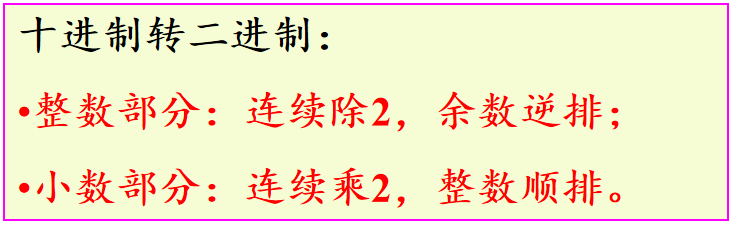

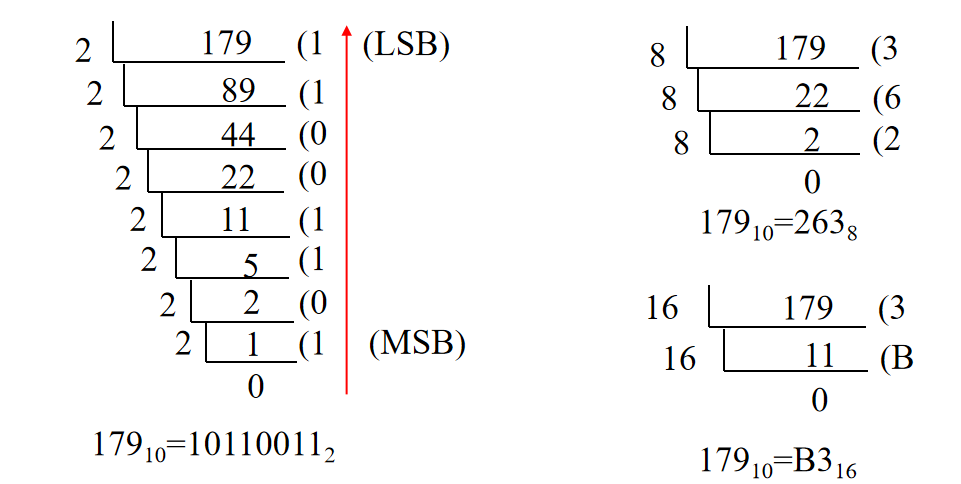

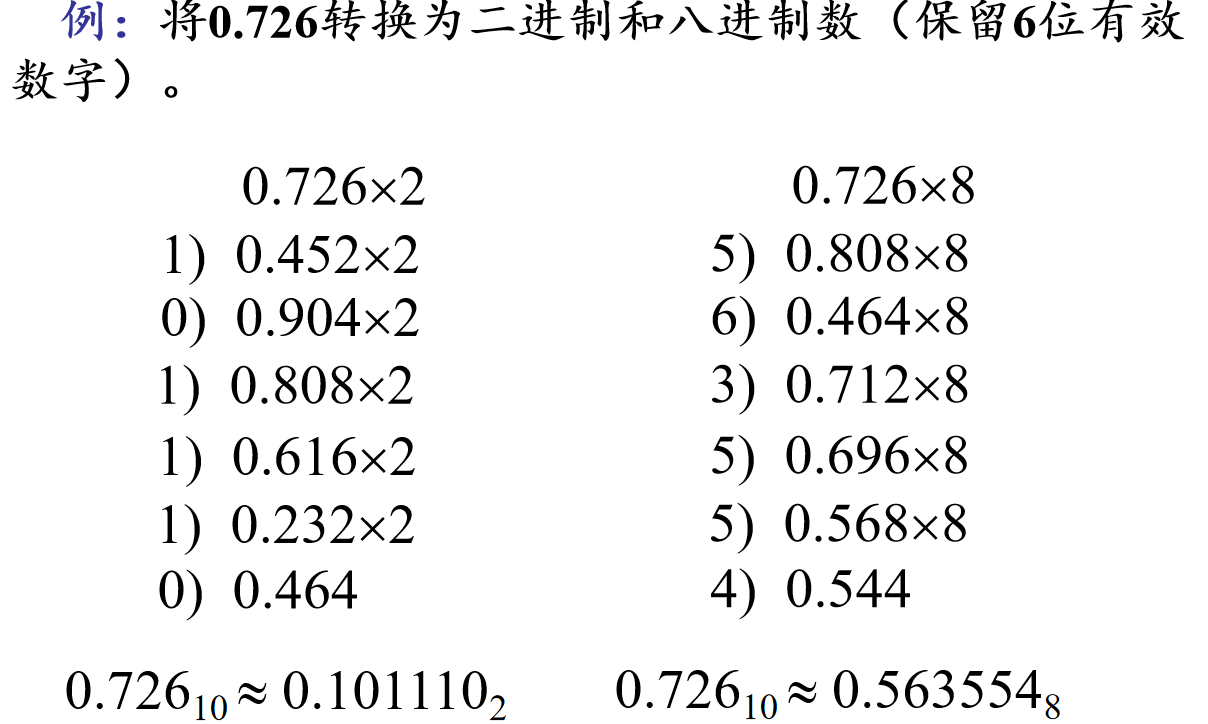

二进制转十进制

A'B'C =

ABC =

最小项最大项性质

① 任意一个最小(大)项,有且仅有一组变量取值使它的值为1(0)。 ②

芯片

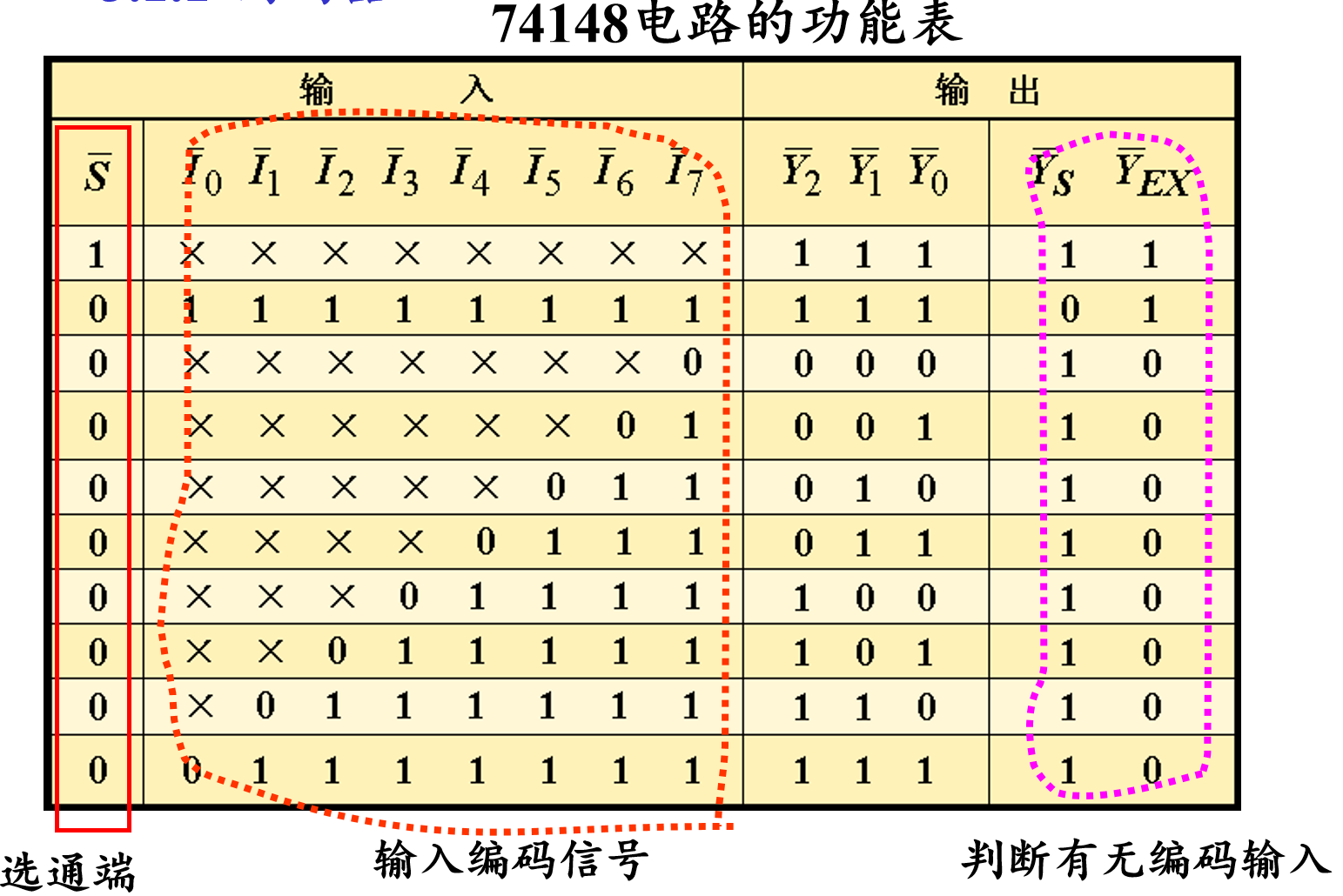

编码器

编码器:输入是一组高、低电平信号,输出是代表不同的事物二进制代码

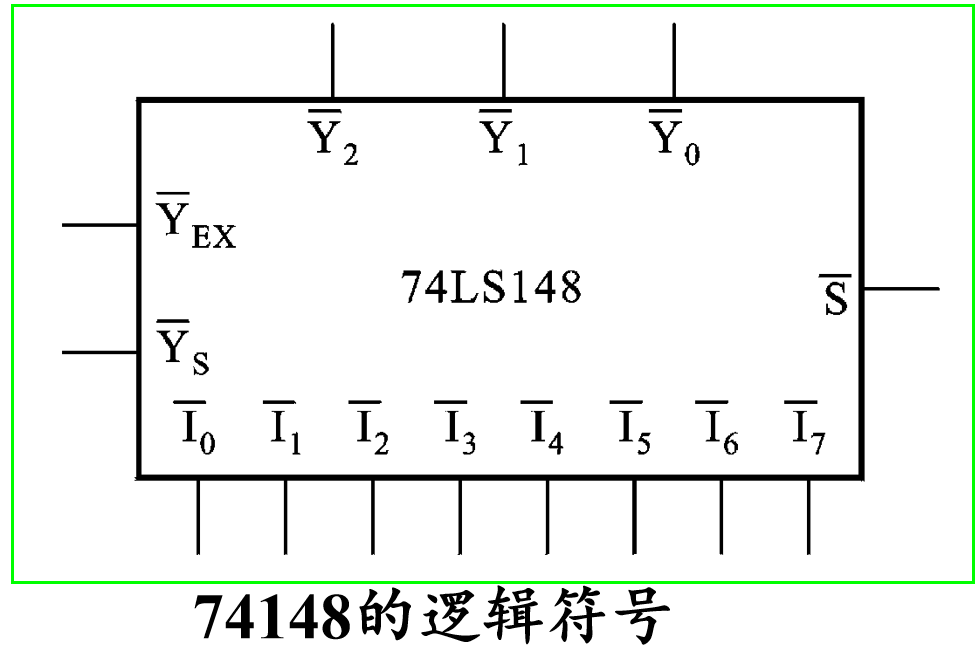

74148芯片

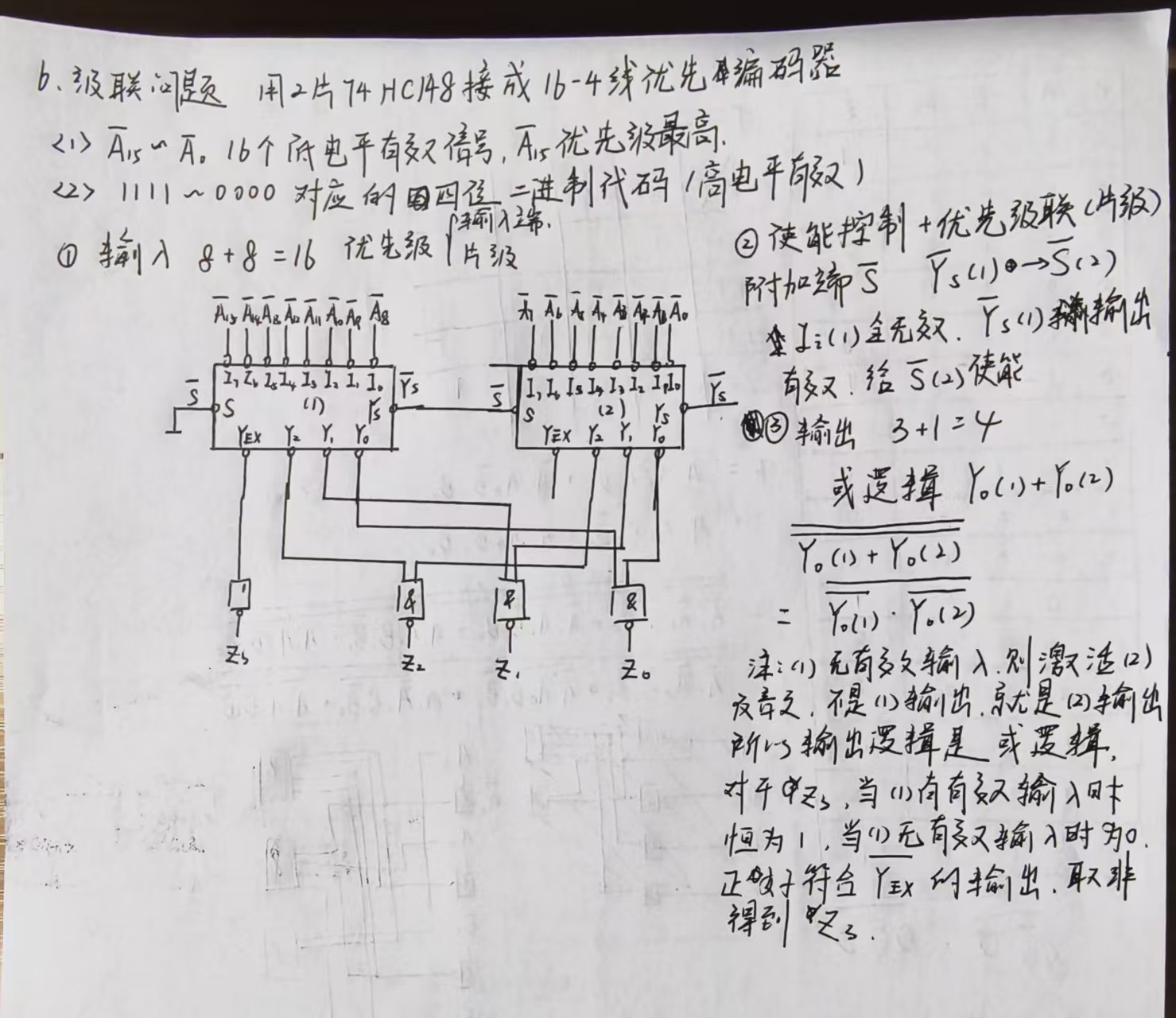

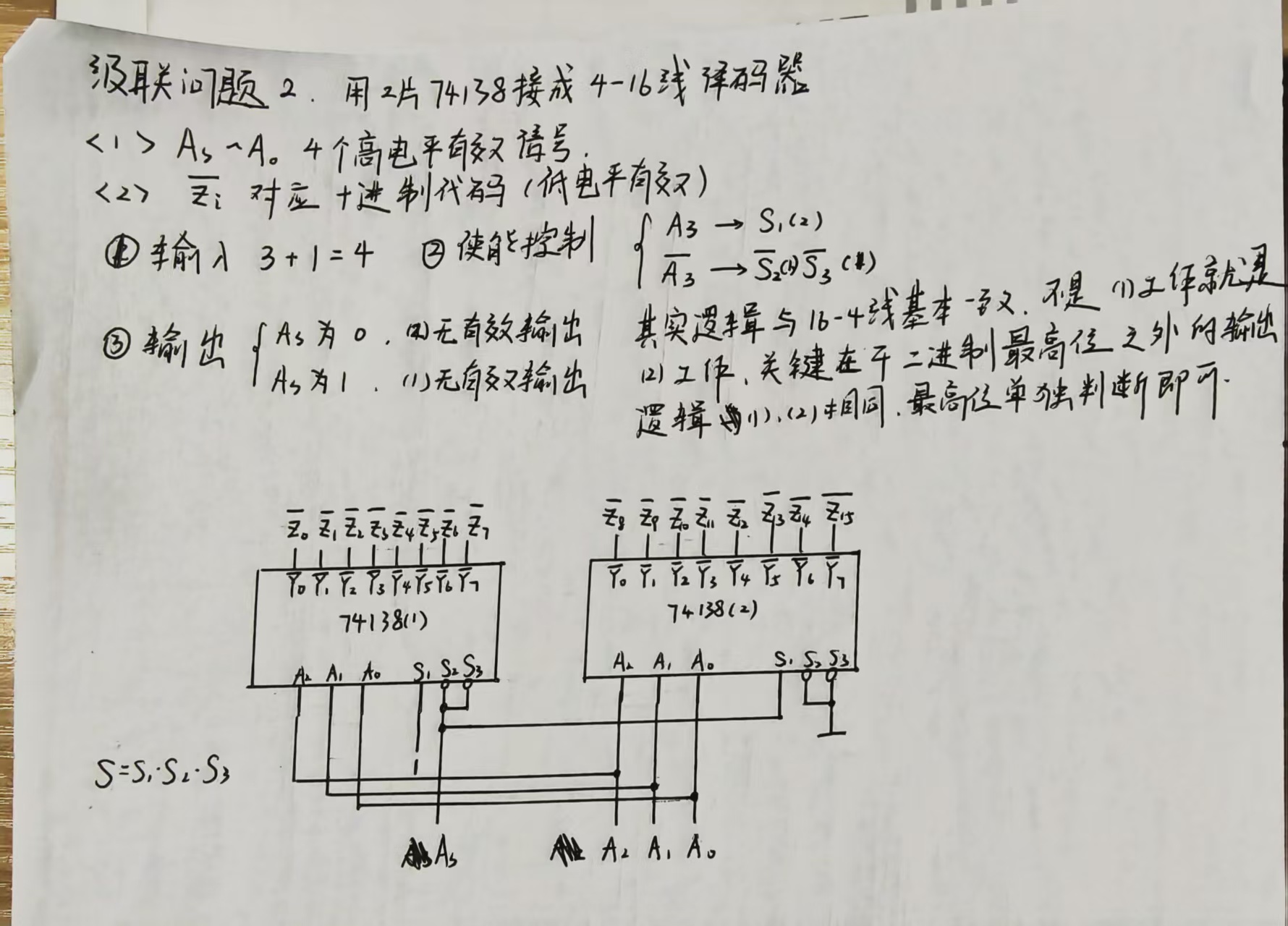

级联为16-4线

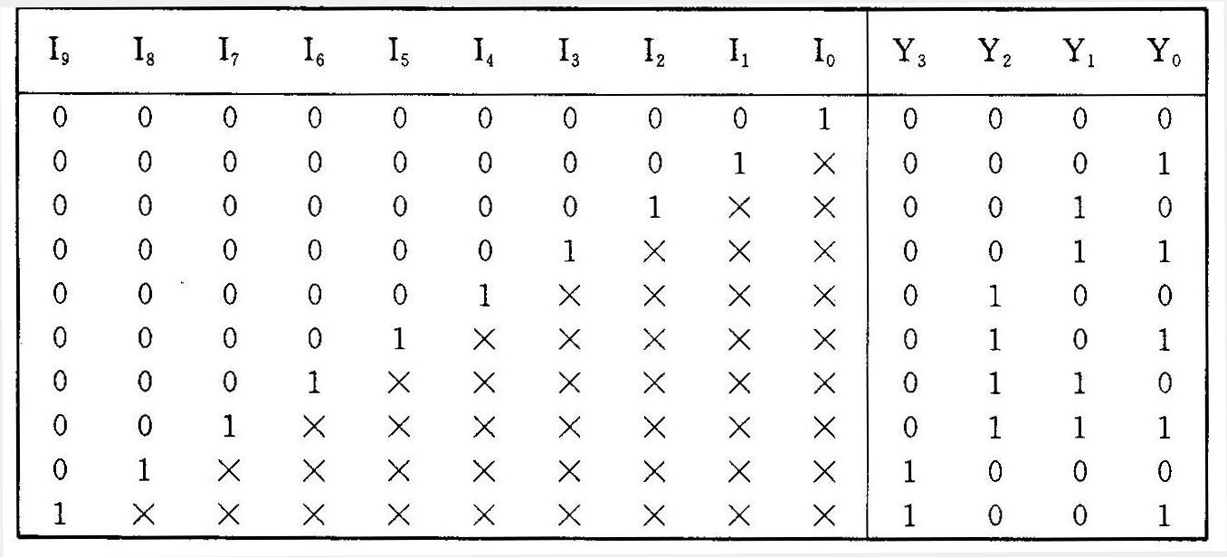

8421BCD编码器

译码器

译码器:输入是一组二进制代码,代表不同的事物,输出是一组高、低电平信号。

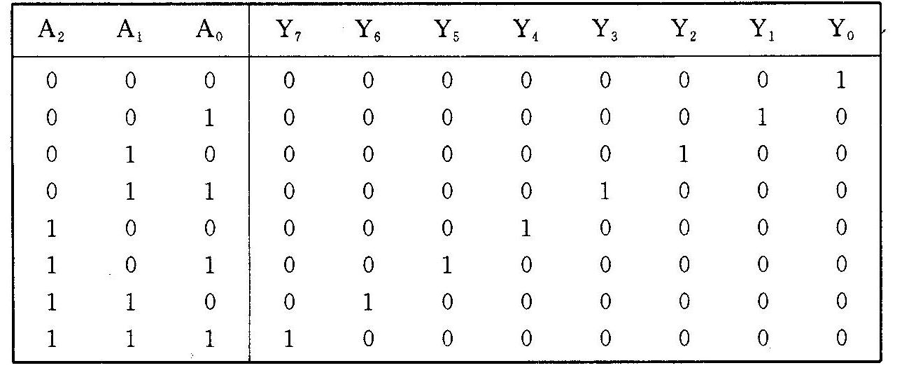

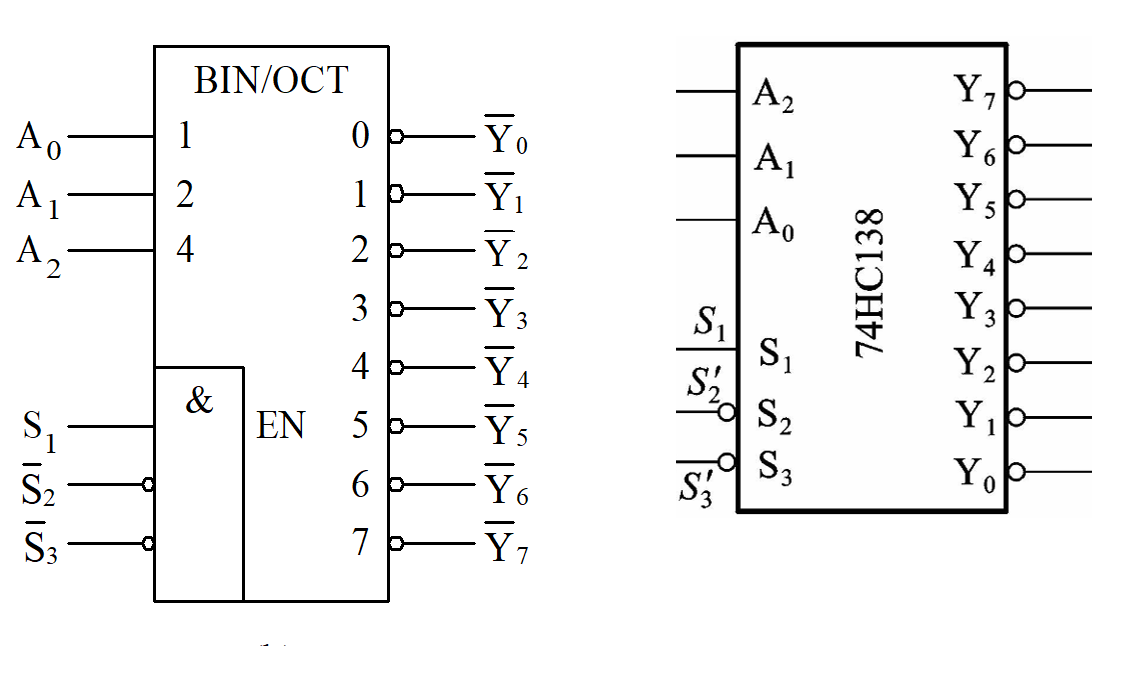

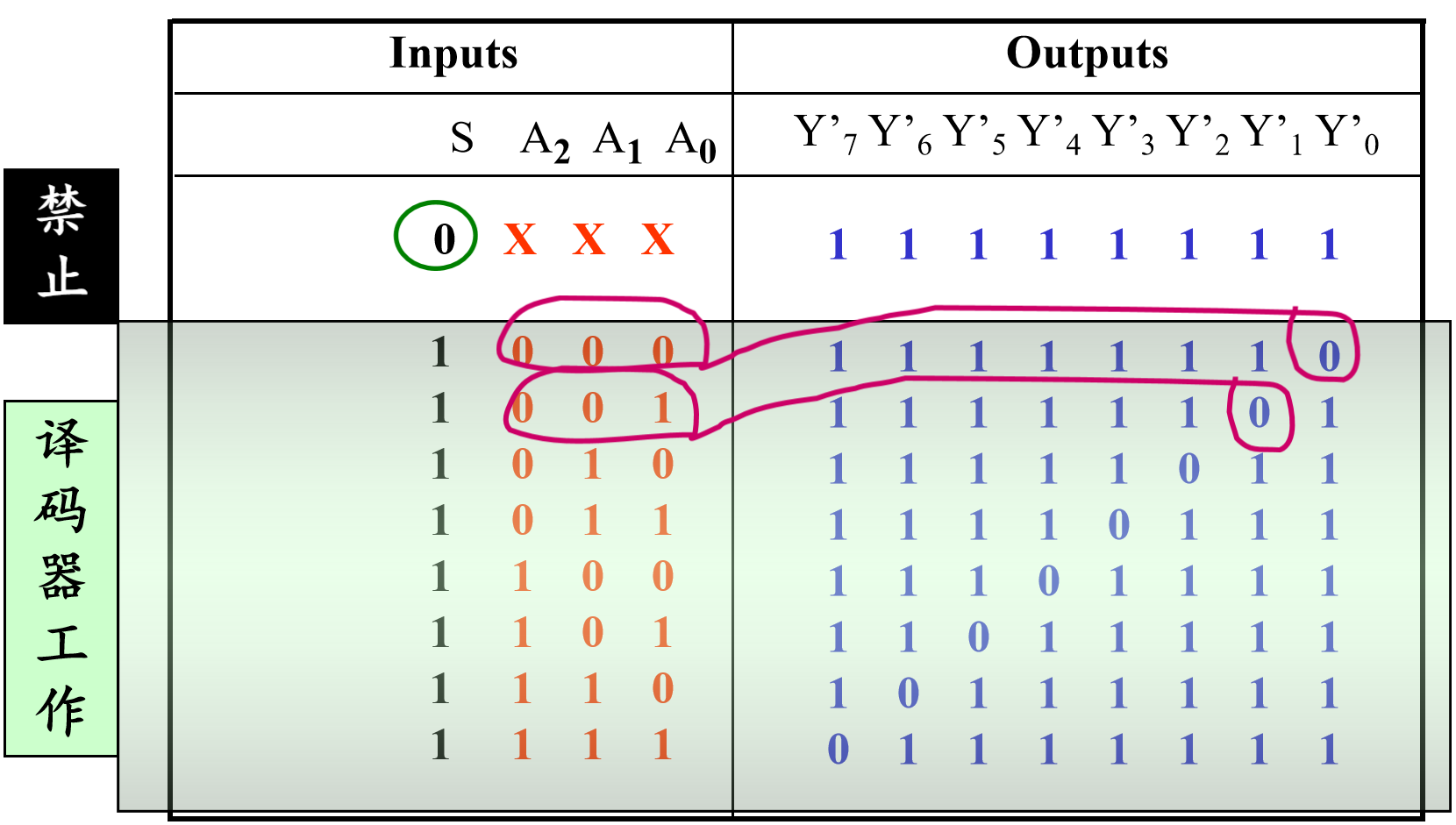

三位二进制译码器

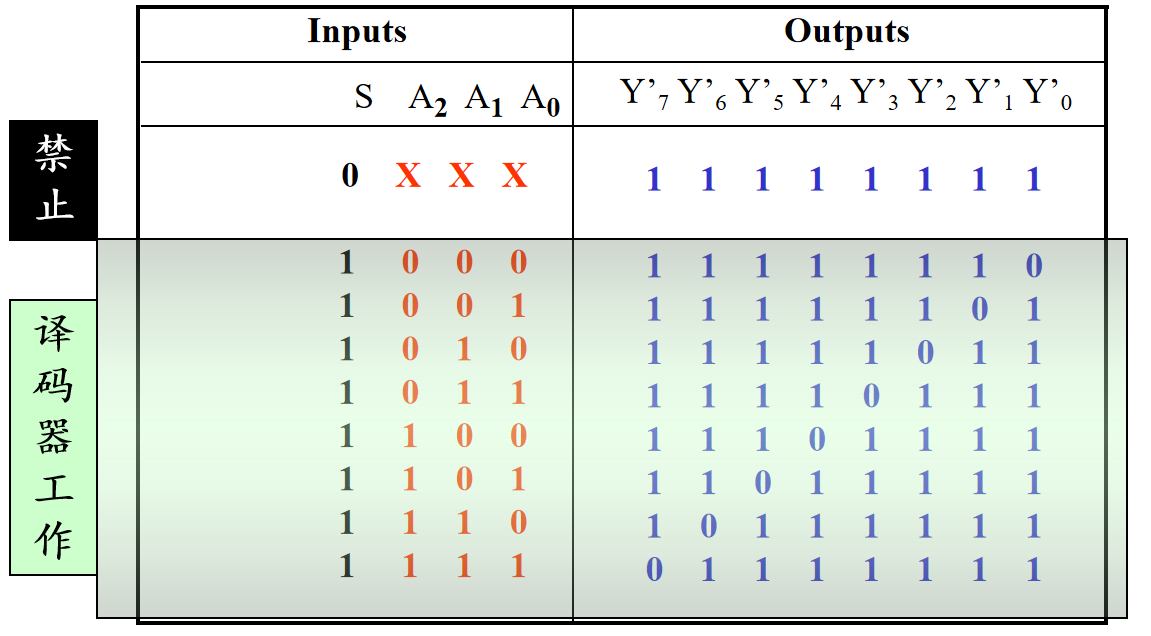

73138译码器

S为控制端(又称使能端), S=1 译码工作; S=0 禁止译码, 输出全1 。

级联为4-16线译码器

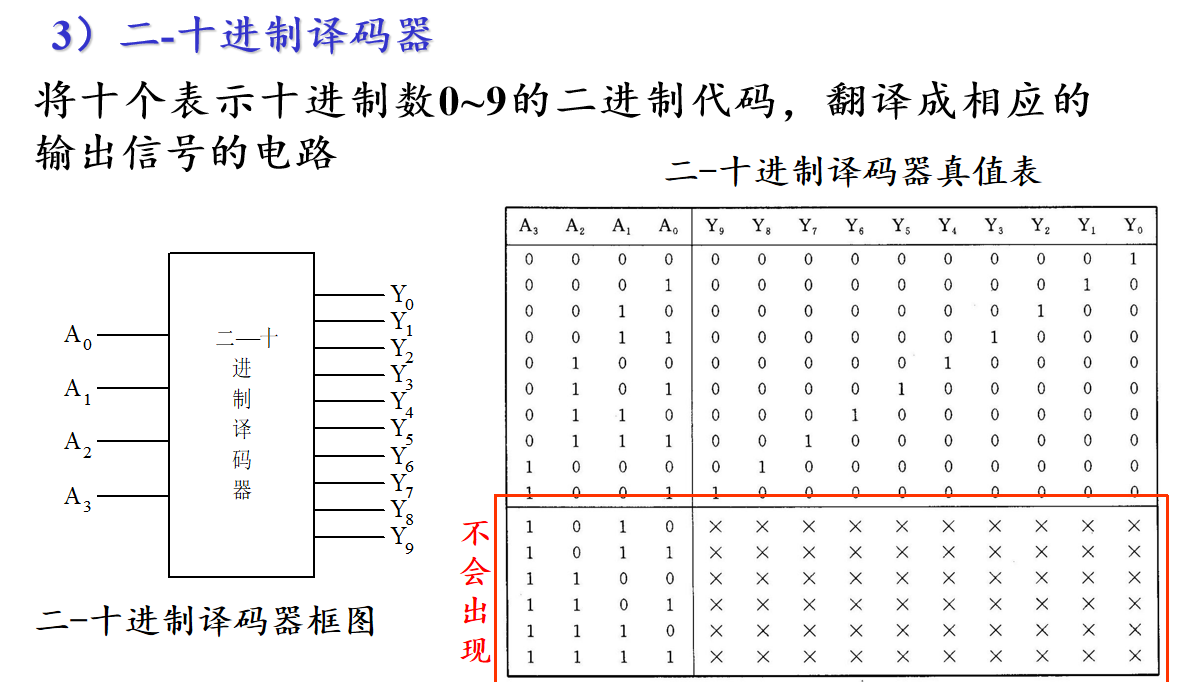

二-十进制译码器

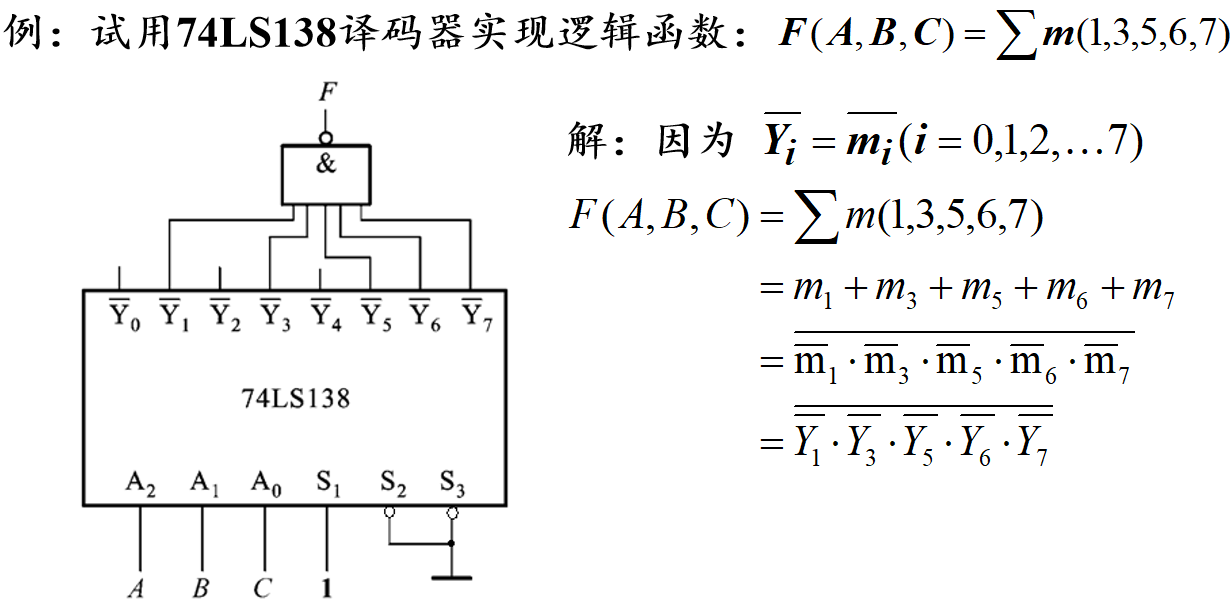

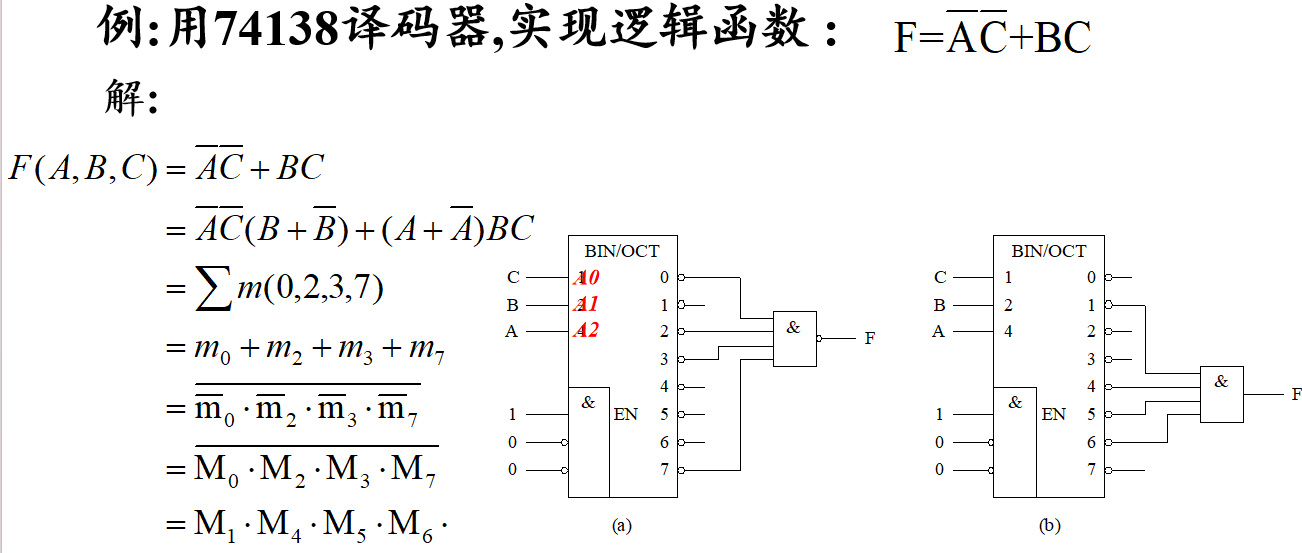

用MSI译码器实现组合逻辑函数

步骤

基本原理

3位二进制译码器给出3变量的全部最小项;

n位二进制译码器给出n变量的全部最小项;

任意函数

将n位二进制译码输出的最小项组合起来,可获得任何形式的输入变量不大于n的组合函数

(1)根据译码器输出特点,将函数转换成相应形式(最小项);

(2)将相应输出端信号进行相或/相与.

【例题】

【例题2】

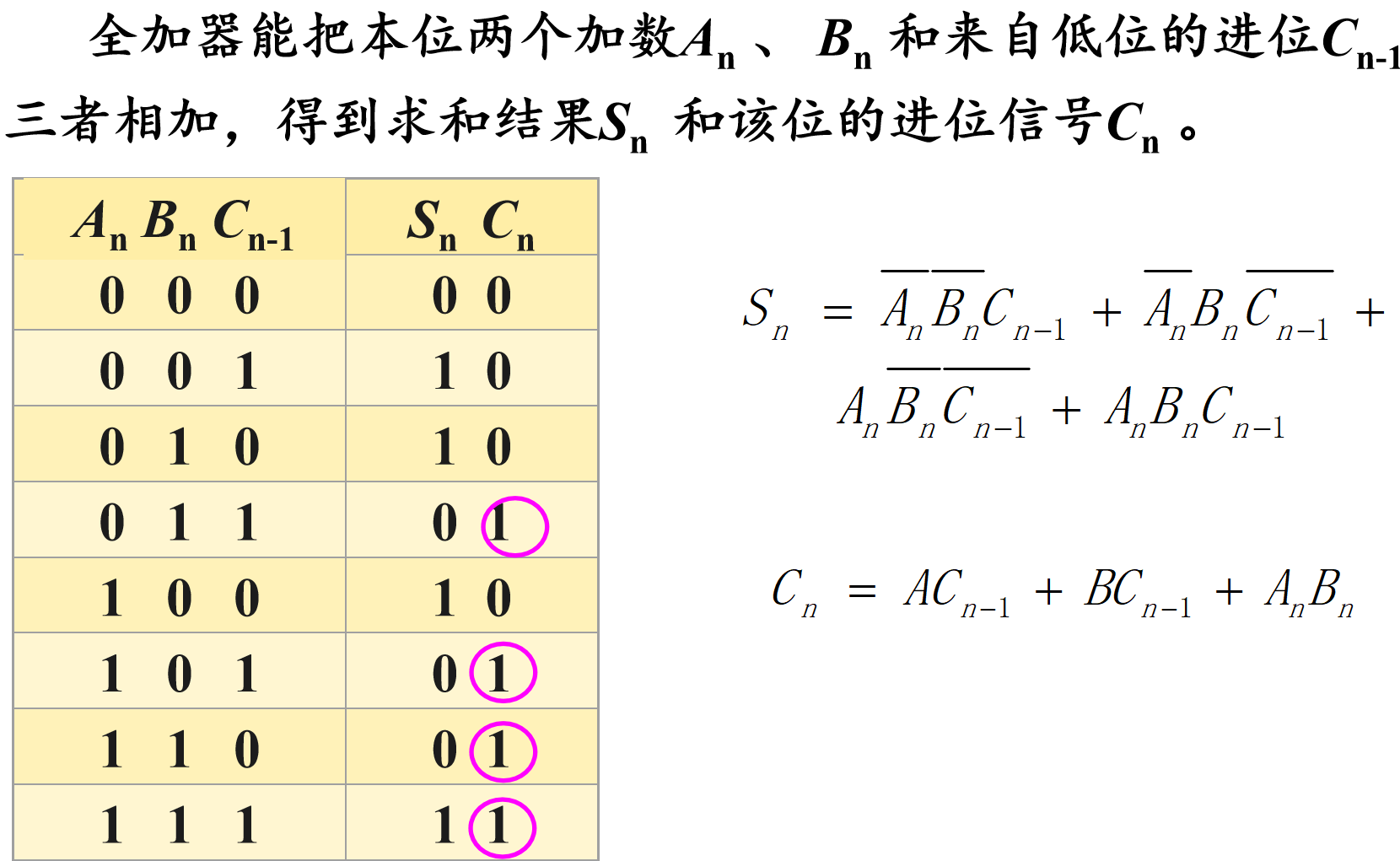

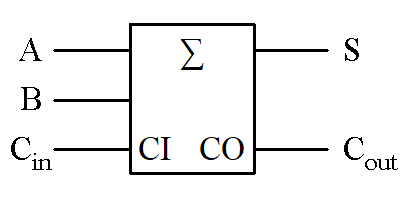

全加器

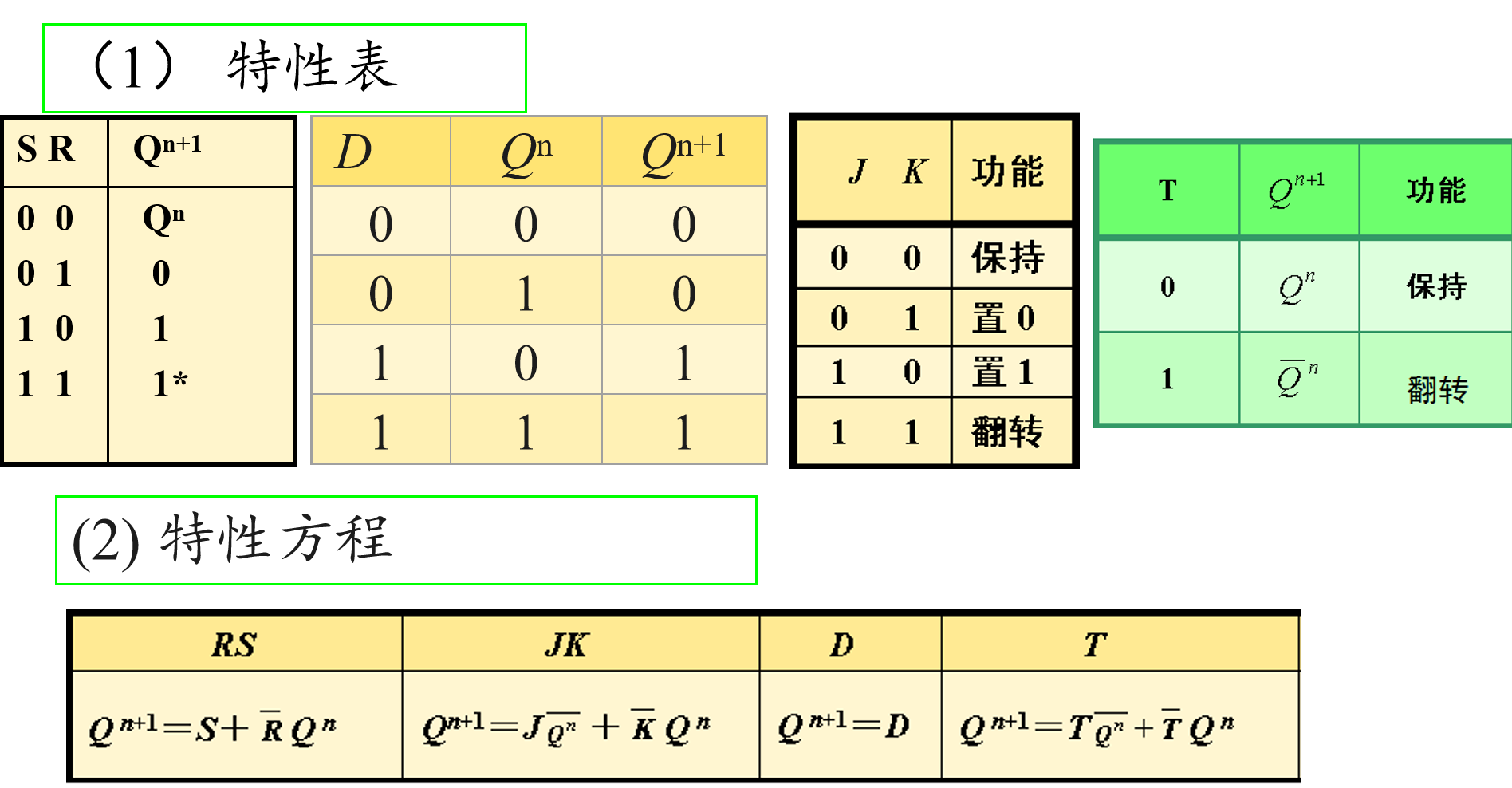

触发器

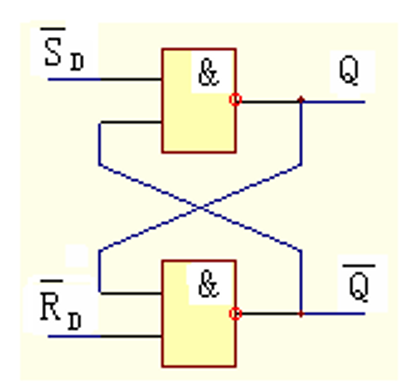

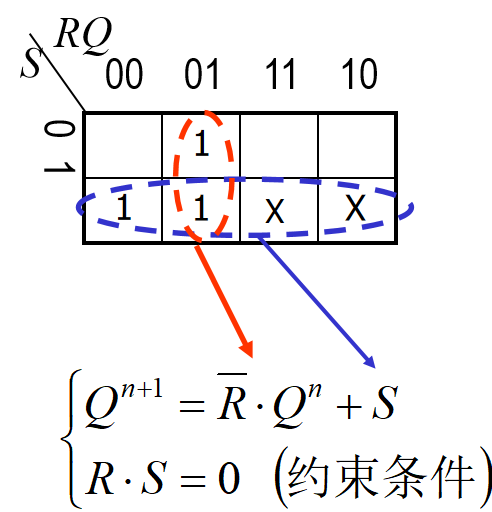

RS触发器

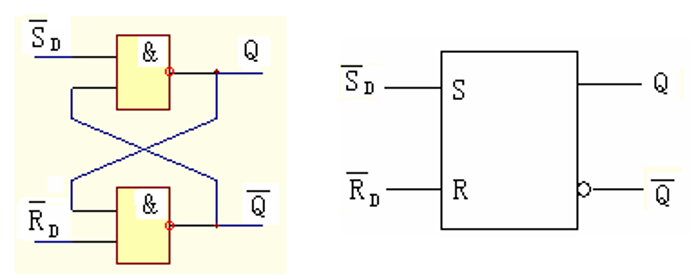

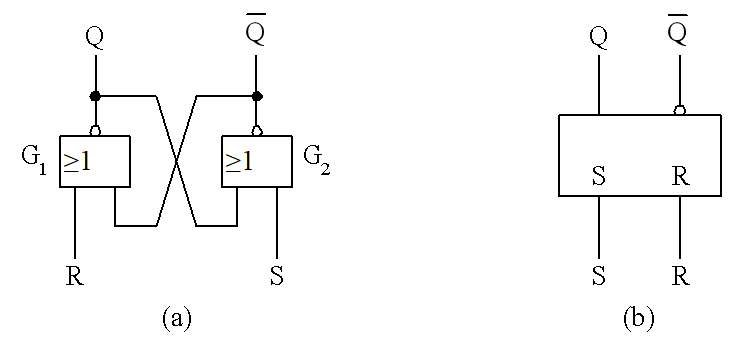

基本触发器

(1)逻辑图

(2)特性表

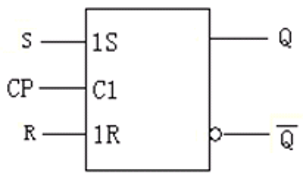

(3)逻辑符号

与非门构成的RS触发器

或非门构成的RS触发器

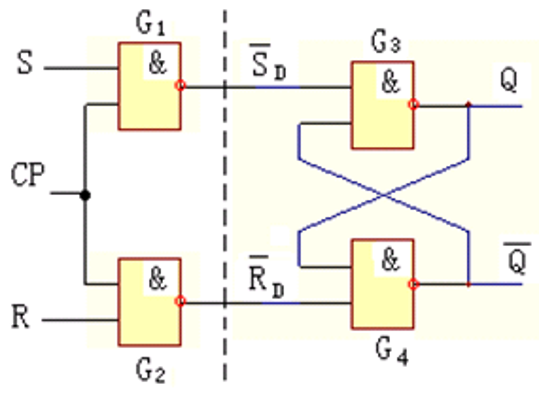

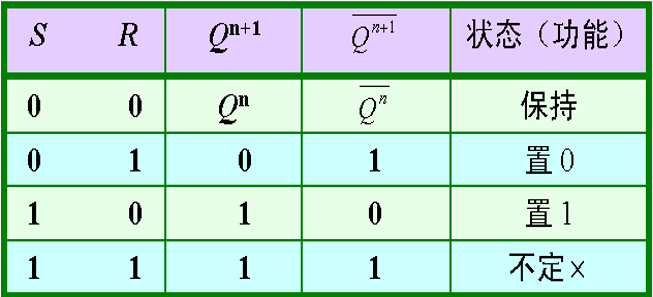

同步RS触发器

(1)逻辑图

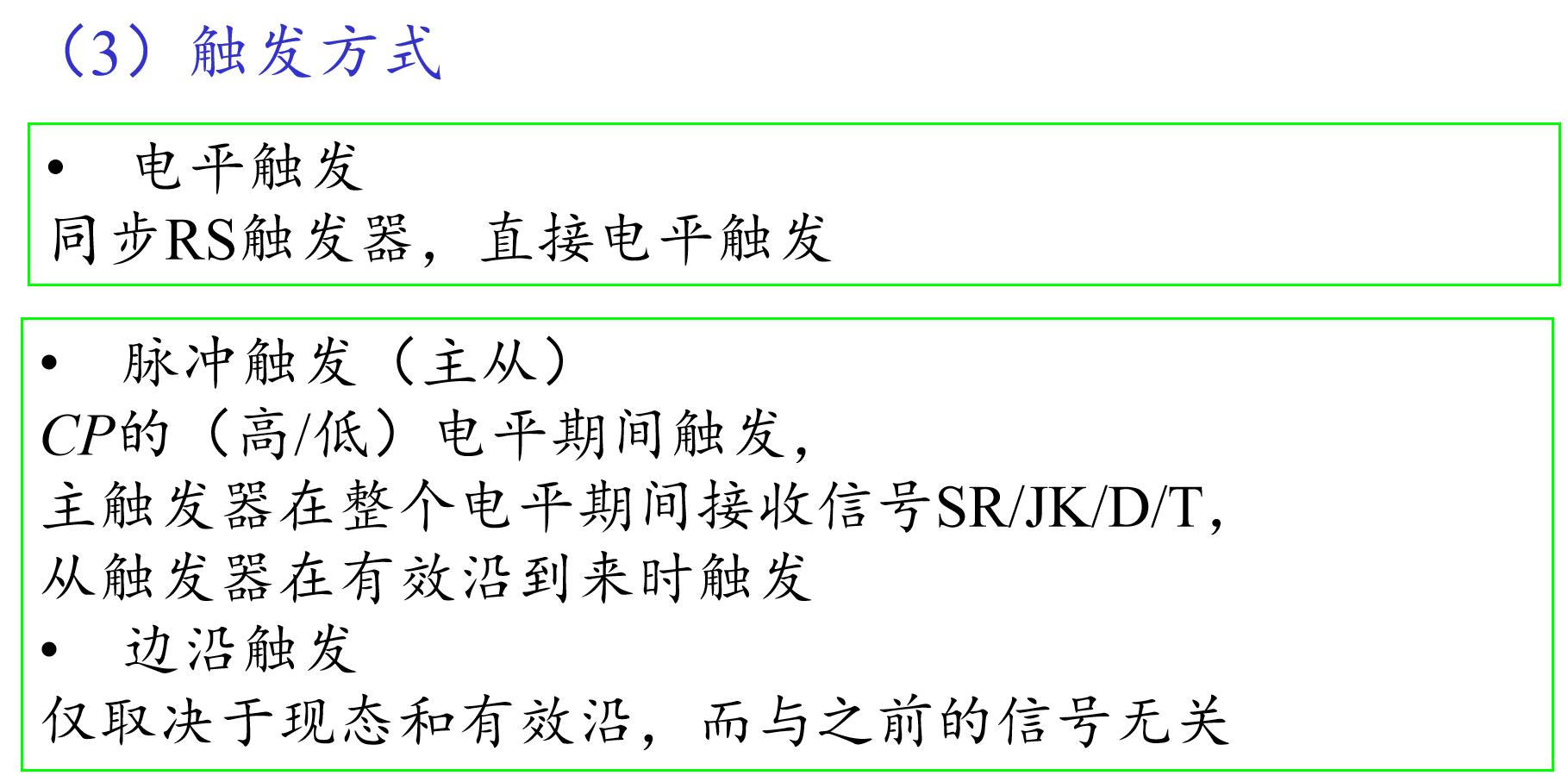

触发方式:电平触发方式,只有CP=1时(高电平有效),触发器的状态才由输入信号R和S来决定。

(2)特性表

S为高电平有效触发

R为高电平有效触发

R、S不允许同时为1(即:约束条件:

(3)逻辑符号

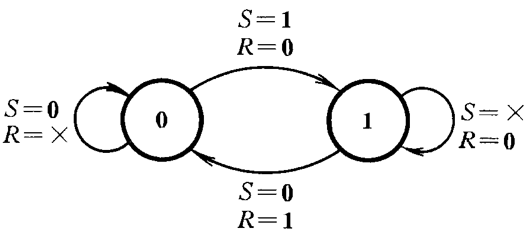

(4)状态转换图

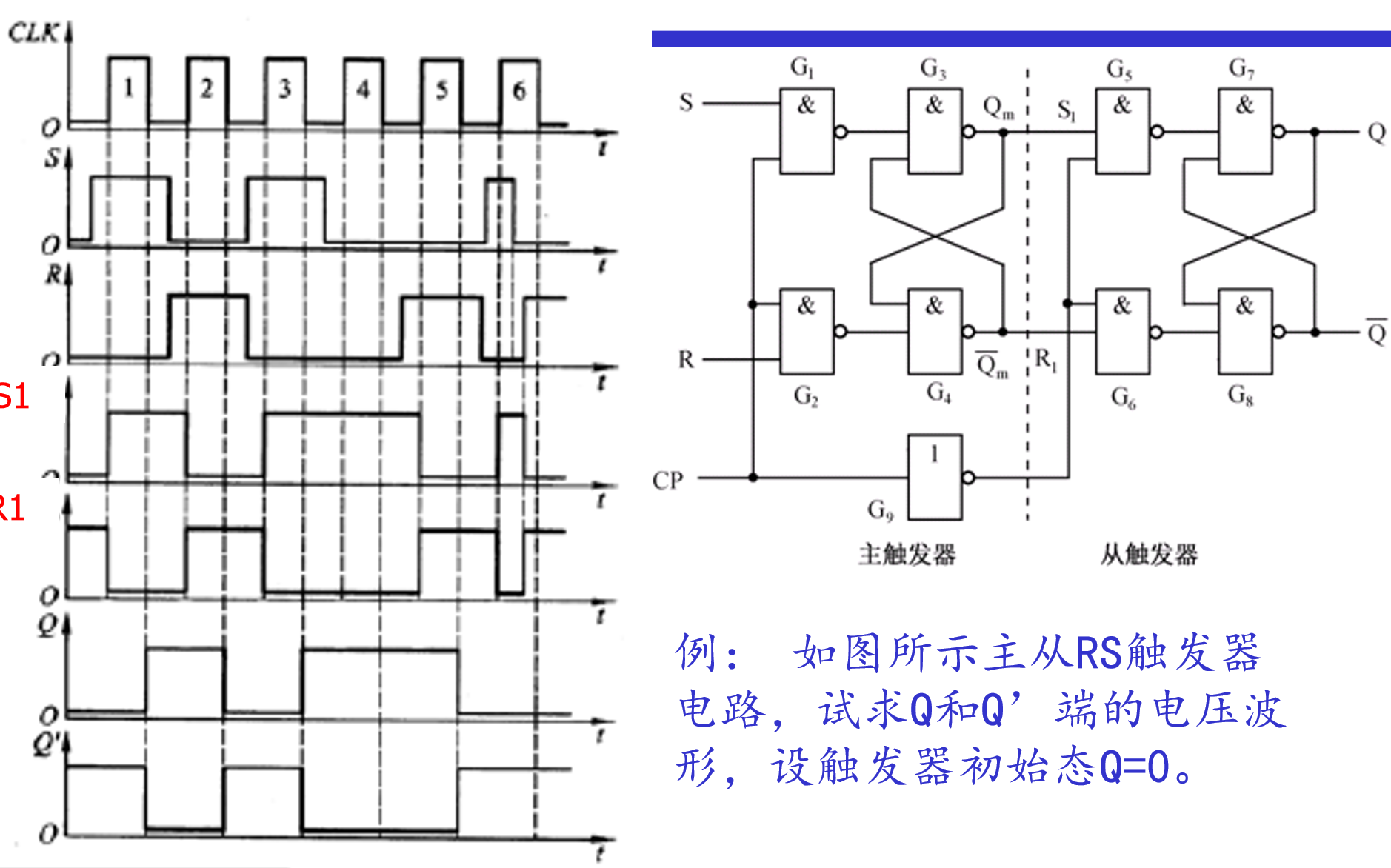

同步主从触发器

先求主触发器的输出,

将主触发器的输出作为输入段,

求出Q

【规律】 主触发器CP = 1接收信号

输出Q下降沿触发

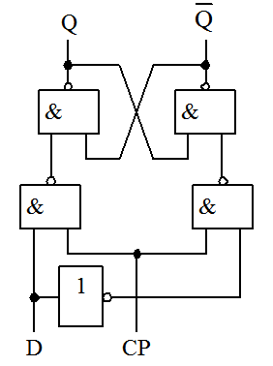

D触发器

D触发器:为了避免R和S同为1的情况出现,在R和S之间加一个非门,这种触发器就是D触发器。

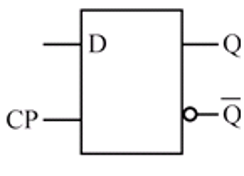

(1)逻辑图

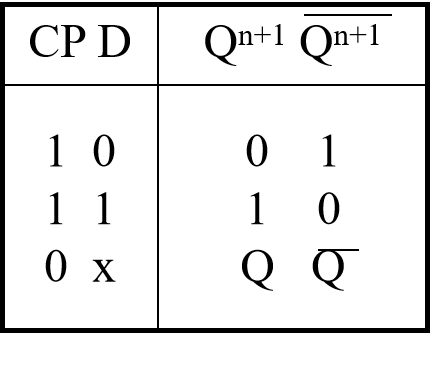

(2)功能表

(3)特征方程

(4)逻辑符号

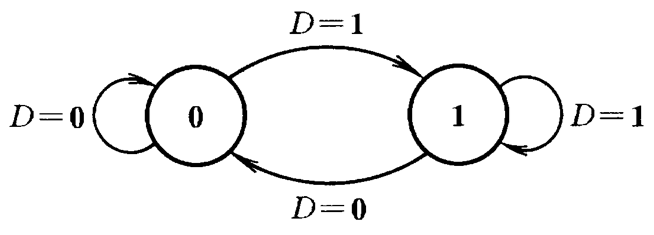

(5)状态转换图

JK触发器

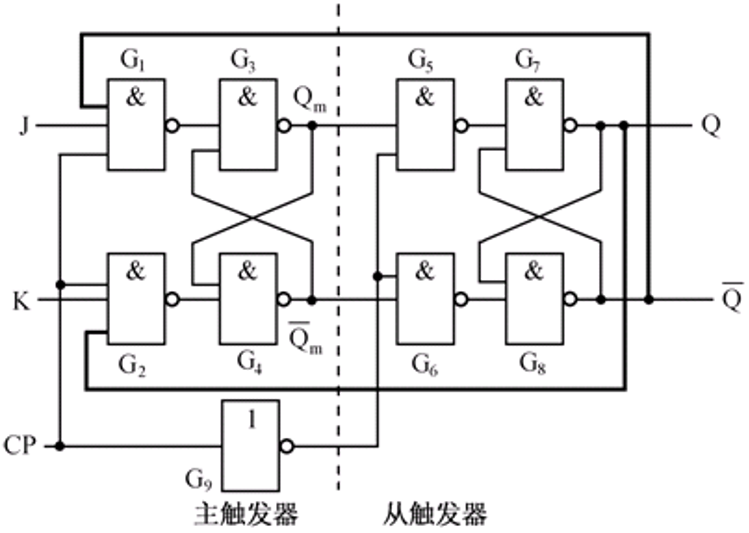

(1)逻辑图

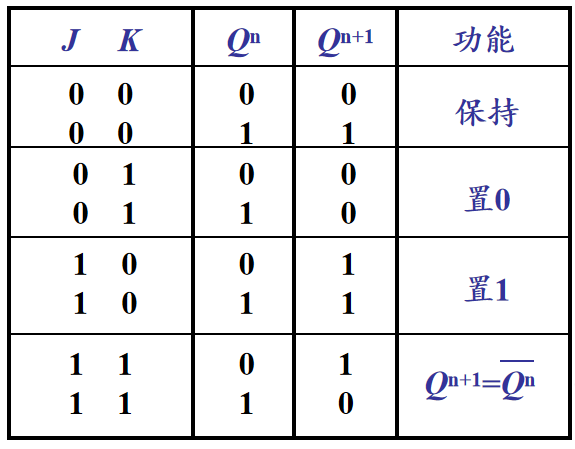

(2)功能表

主触发器在CP=1期间均可以接收输入信号,从触发器的状态只在CP从1->0时发生变化。

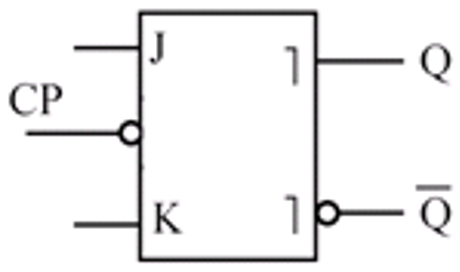

(3)逻辑符号

(4)特征方程

T触发器

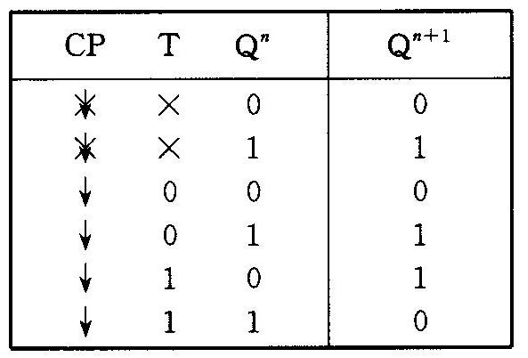

(2)特性表

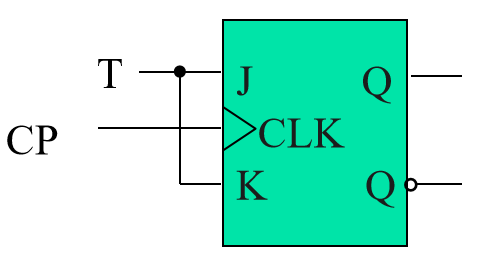

(3)逻辑符号

(4)特征方程

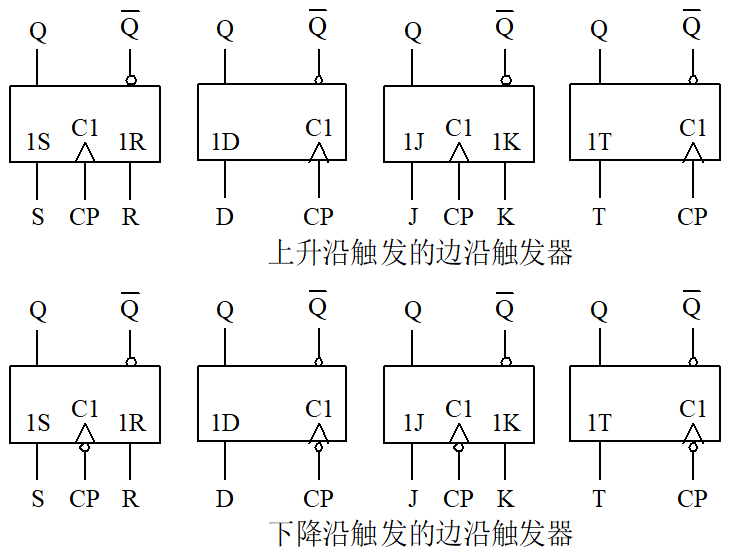

边沿触发器

触发器总结

芯片总结

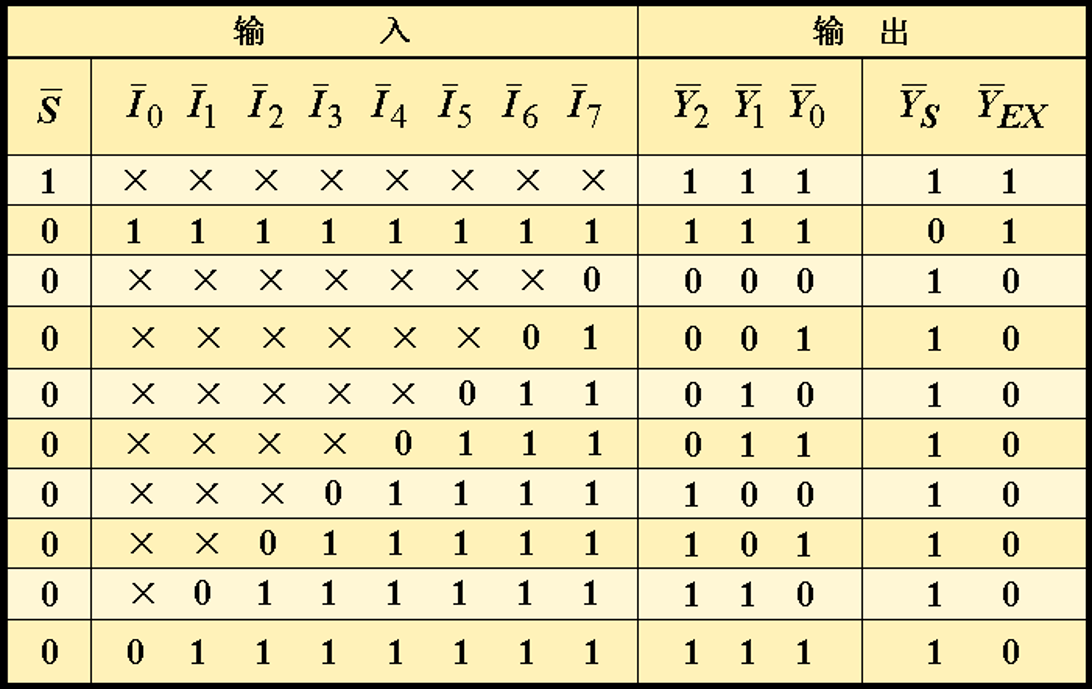

8线-3线优先编码器74148

8线-3线优先编码器74148

3线-8线译码器74138

S为控制端(又称使能端), S=1 译码工作; S=0 禁止译码, 输出全1。

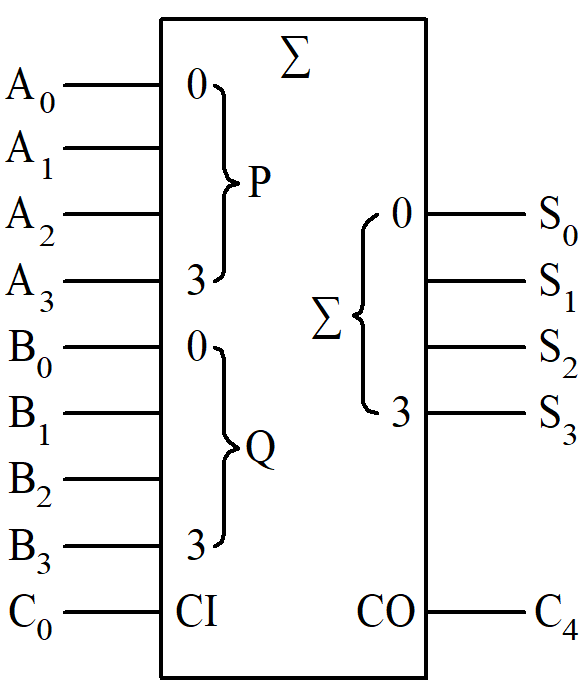

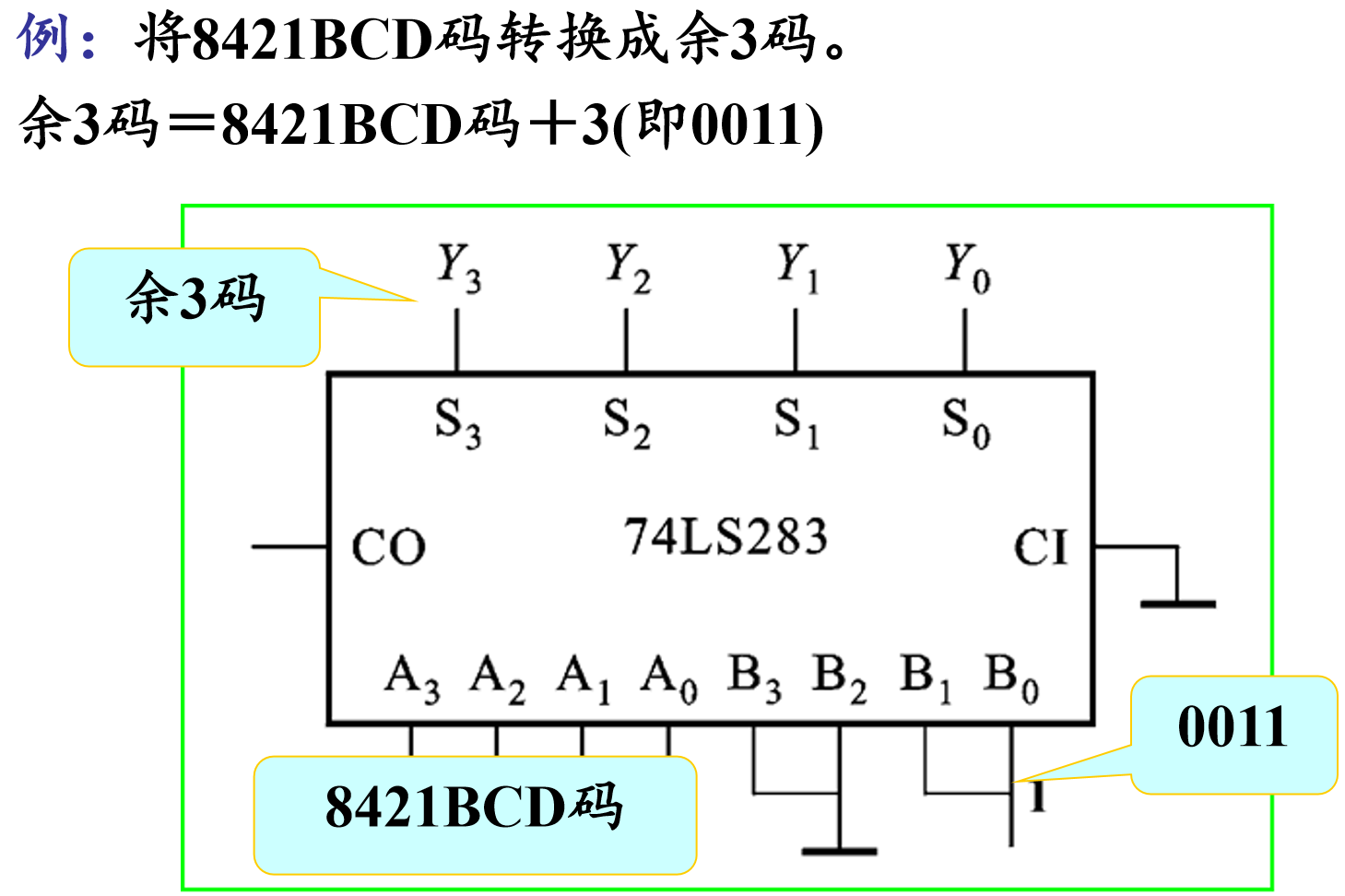

全加器

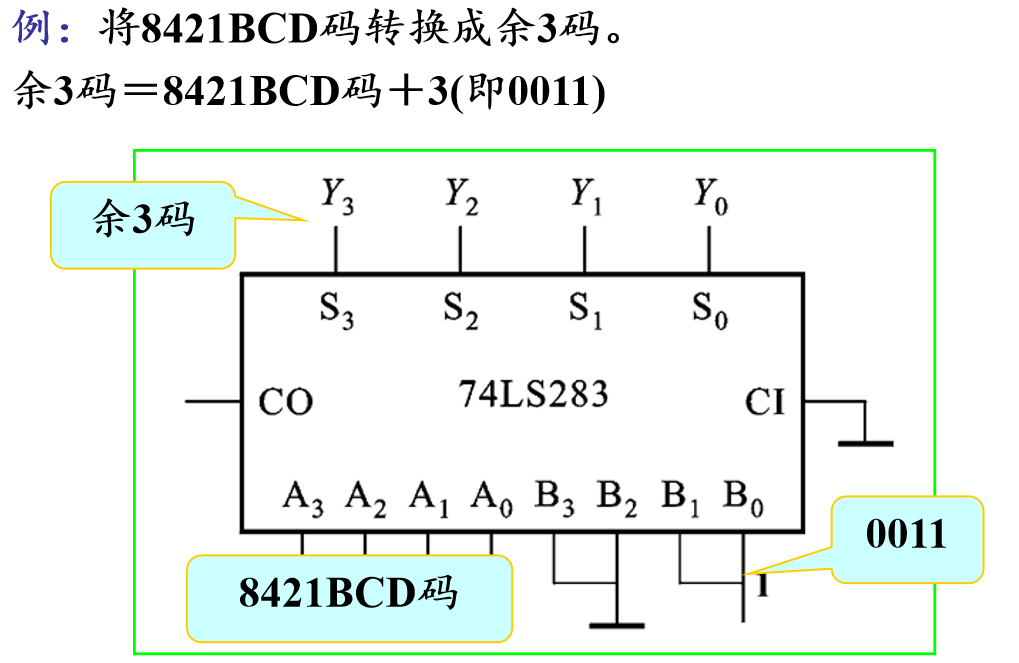

MSI74283加法器

四位二进制超前进位加法器

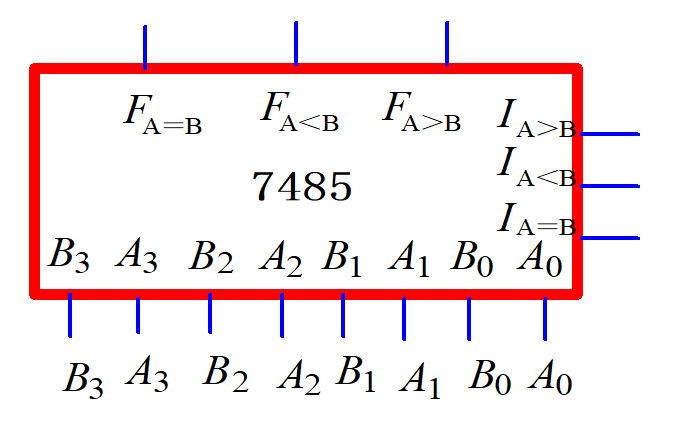

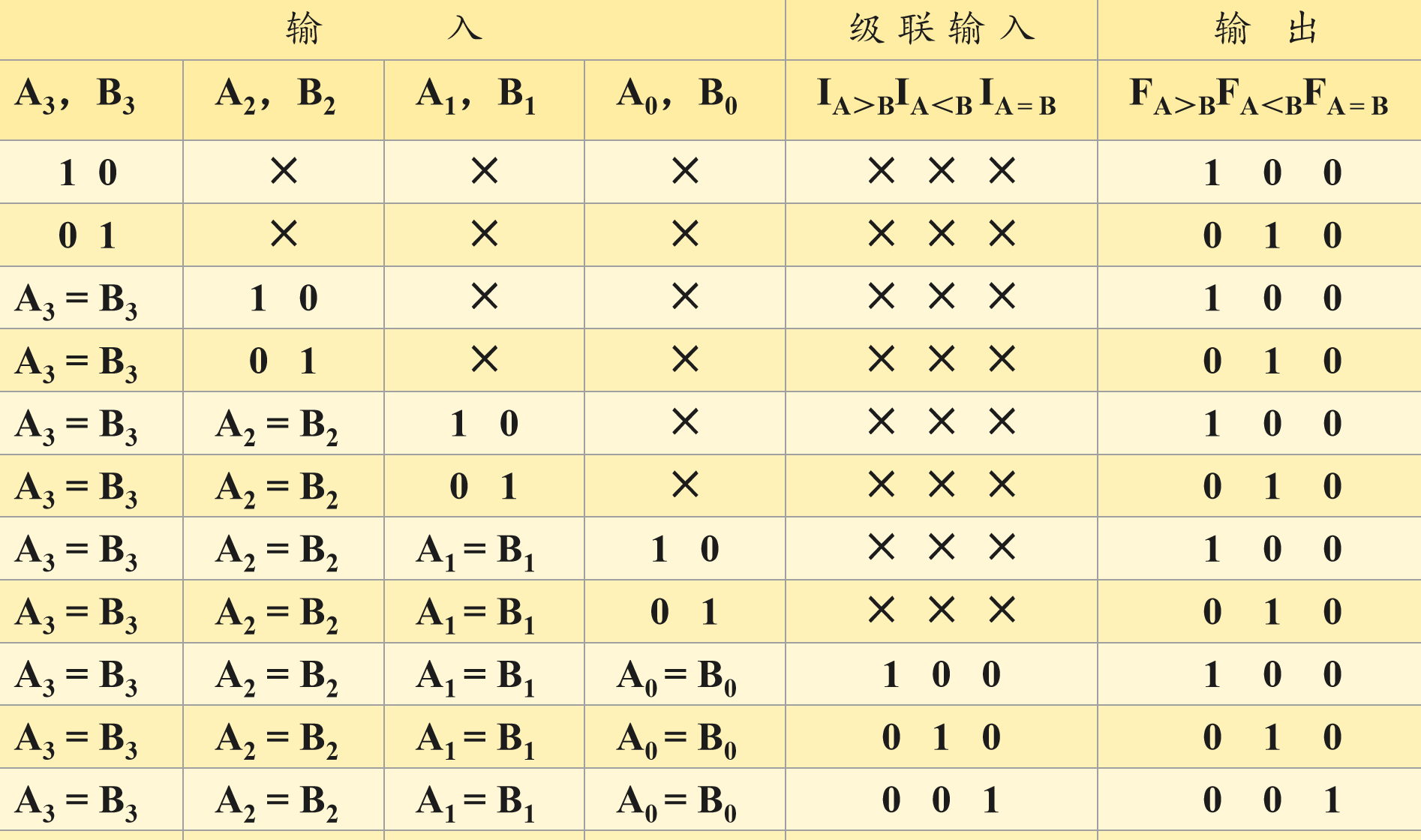

MSI7485比较器

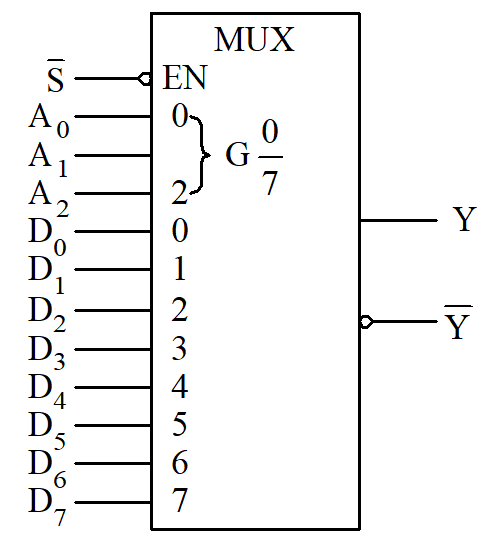

74151八选一数据选择器

74153四选一数据选择器

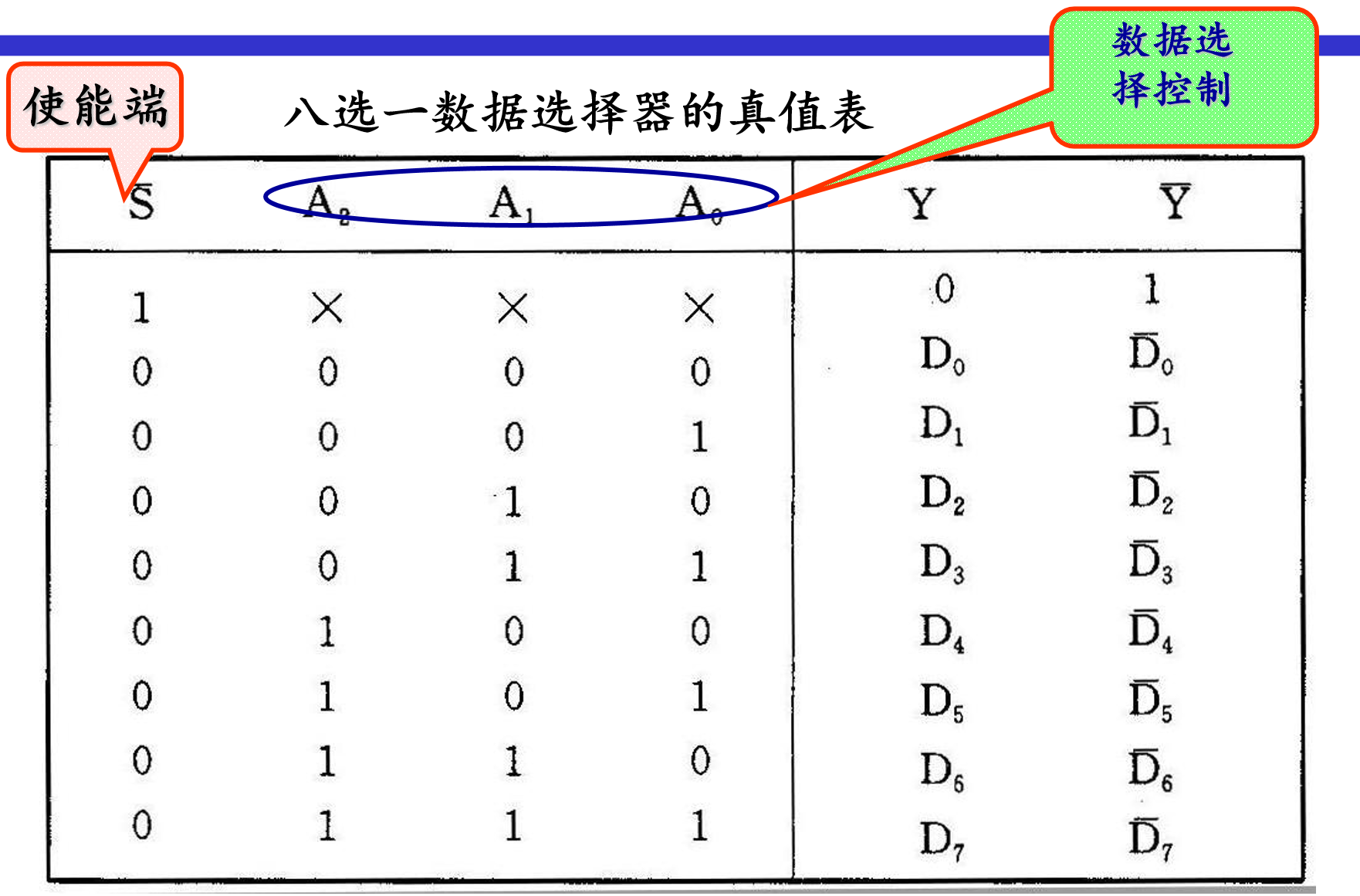

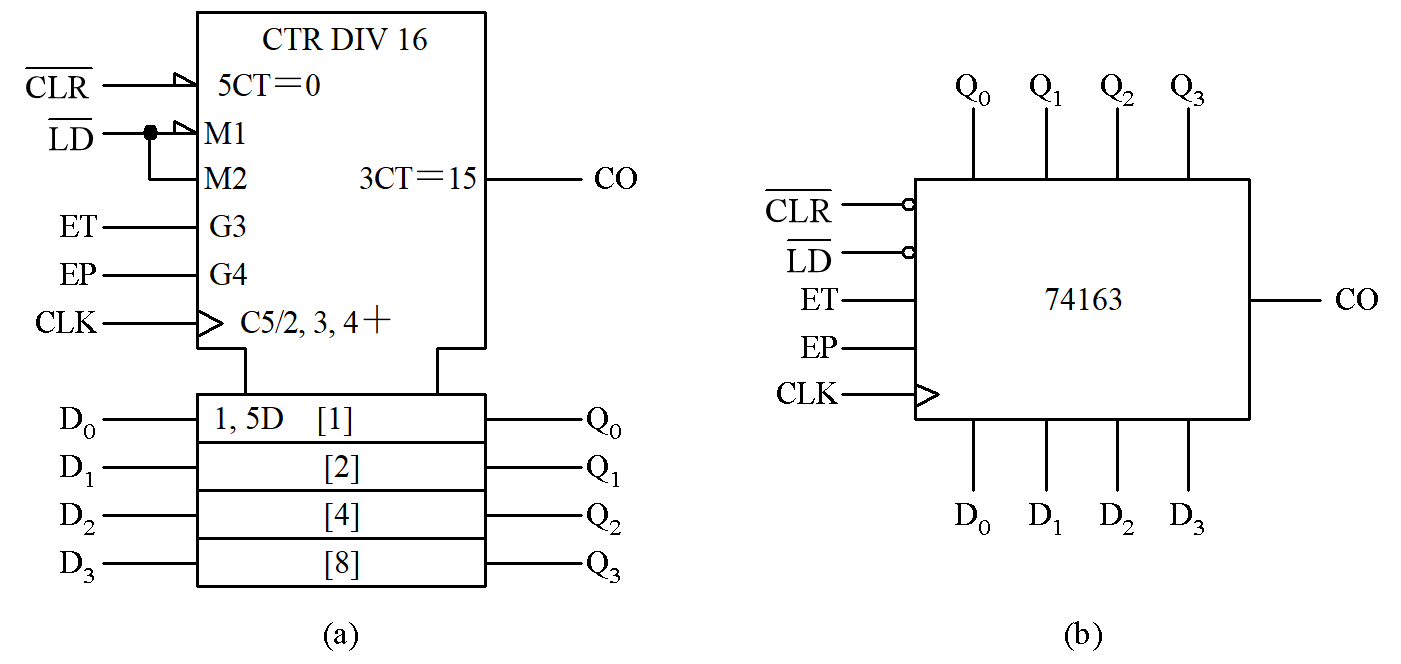

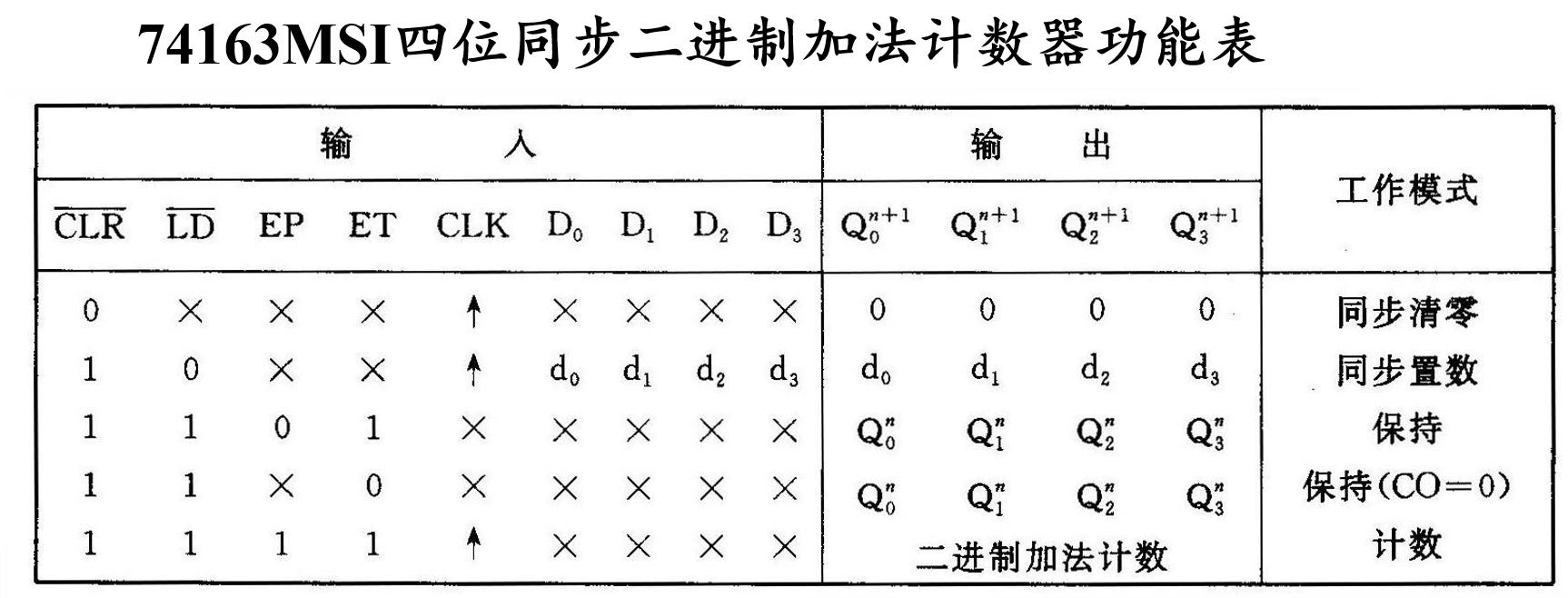

74163计数器

74163是中规模集成四位同步二进制加法计数器,计数范围是0~15。它具有同步置数、同步清零、保持和二进制加法计数等逻辑功能。

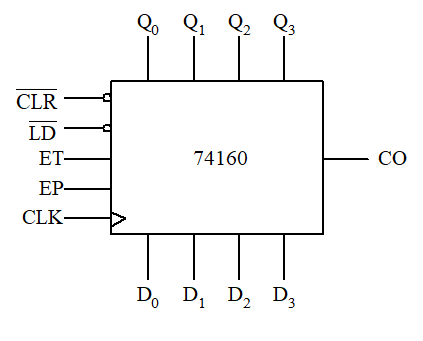

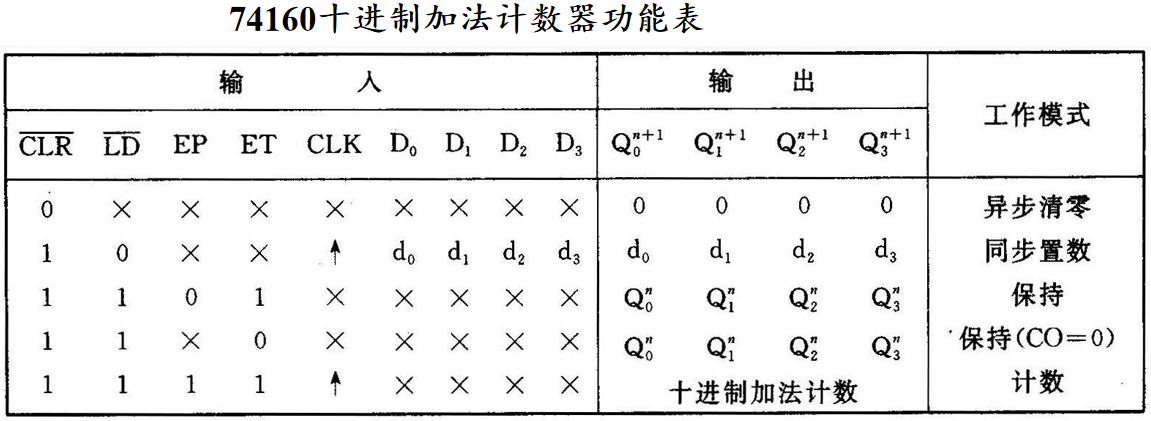

74160计数器

74160是中规模集成8421BCD码同步十进制加法计数器,计数范围是0~9。它具有同步置数、异步清零、保持和十进制加法计数等逻辑功能。

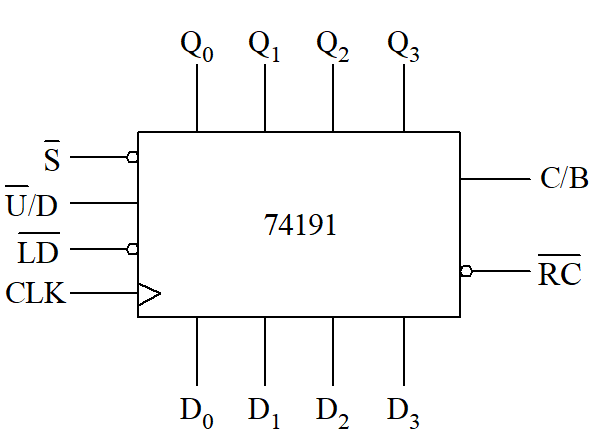

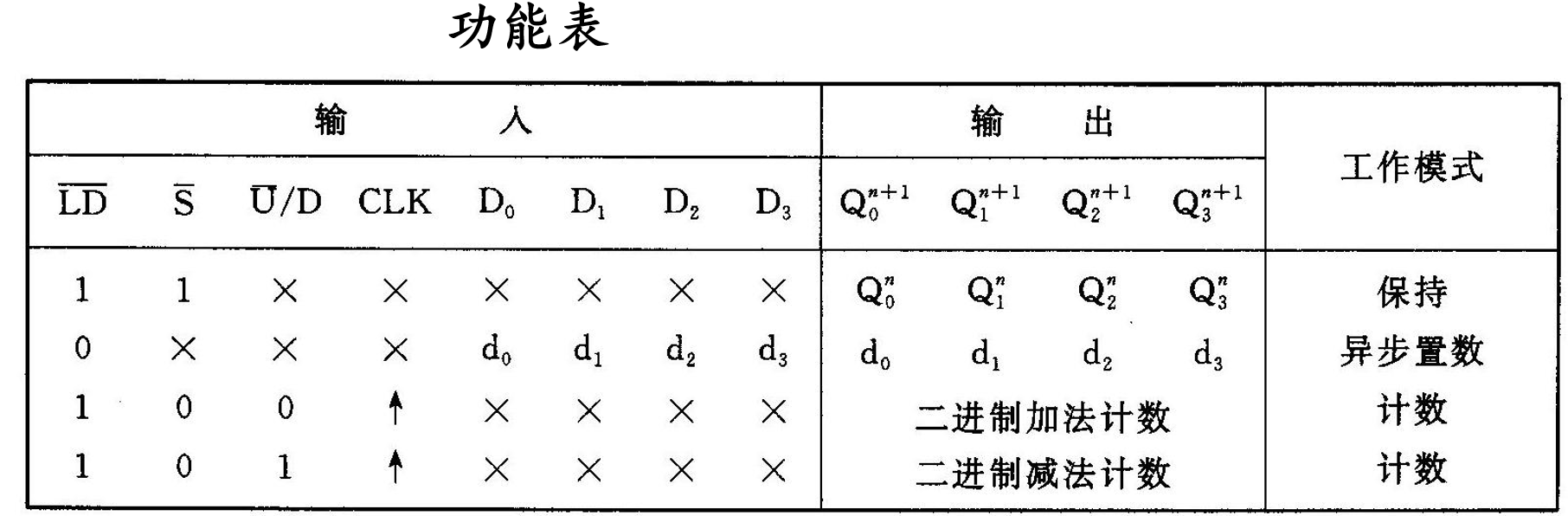

74191计数器

74191是中规模集成四位单时钟同步二进制加/减可逆计数器,计数范围是0~15。它具有异步置数、保持、二进制加法计数和二进制减法计数等逻辑功能。

数模/模数转换

数模转换器

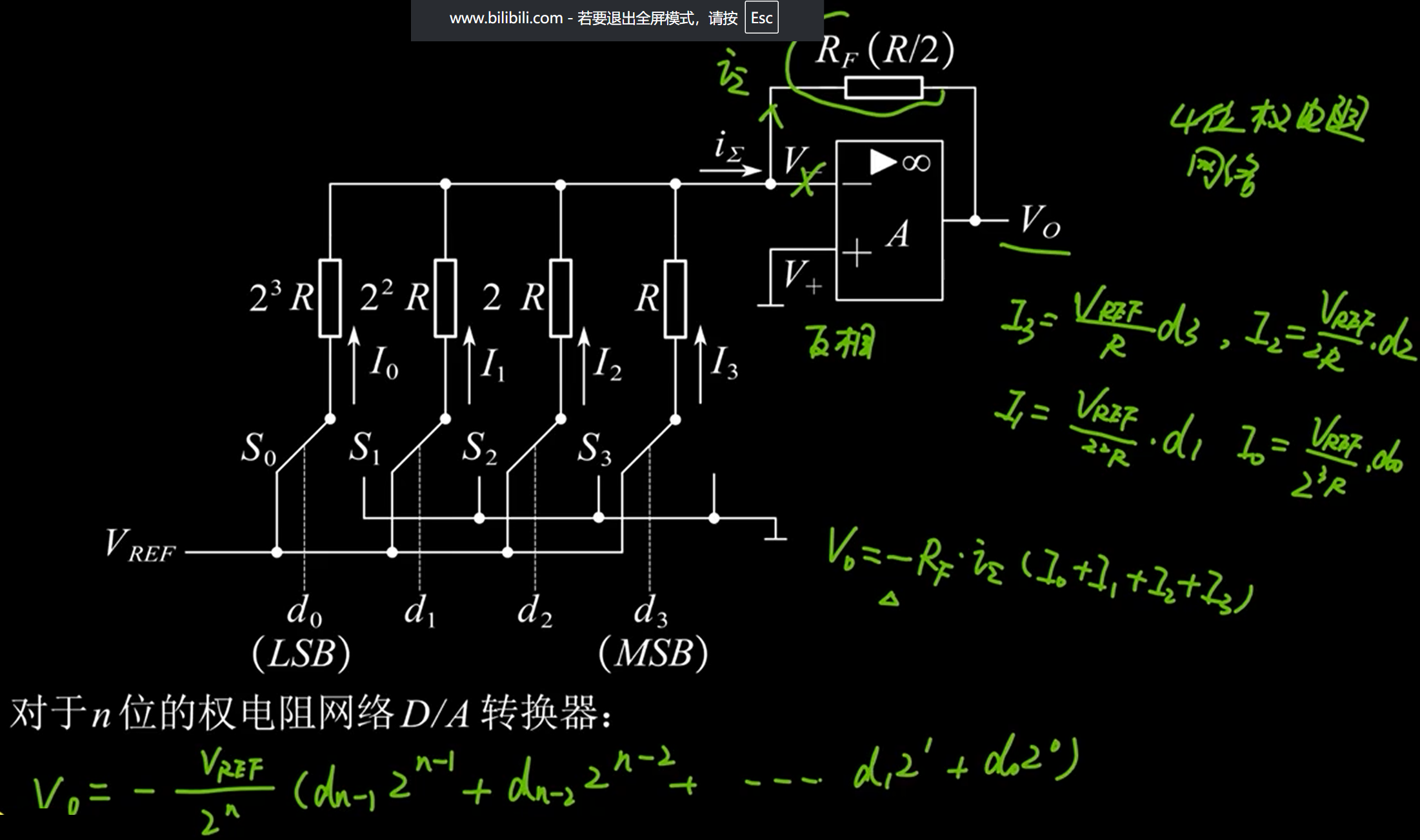

n位权电阻网络D/A转换器:

特点:结构比较简单,所用的电阻元件数很少。

缺点:各个电阻的阻值相差较大,尤其在输入信号的位数较多时,这个问题就更加突出。